# NET+50 Hardware Reference

90000281\_C

# NET+50 Hardware Reference

Part number/version: 90000281\_C

Release date: March 2006

www.digi.com

©2001-2006 Digi International Inc.

Printed in the United States of America. All rights reserved.

Digi, Digi International, the Digi logo, the Making Device Networking Easy logo, NetSilicon, a Digi International Company, NET+, NET+OS and NET+Works are trademarks or registered trademarks of Digi International, Inc. in the United States and other countries worldwide. All other trademarks are the property of their respective owners.

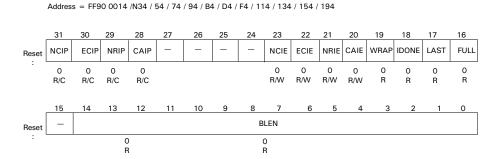

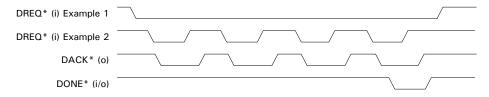

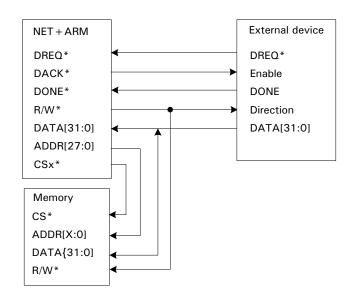

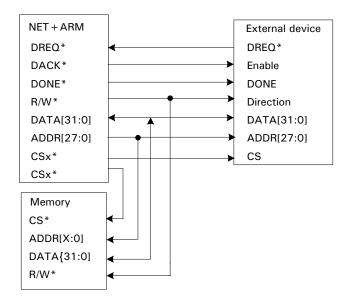

Information in this document is subject to change without notice and does not represent a committment on the part of Digi International.

Digi provides this document "as is," without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of, fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are made periodically to the information herein; these changes may be incorporated in new editions of the publication.

Digi International 11001 Bren Road East Minnetonka, MN 55343 U.S.A. United States: +1 877 912-3444 Other locations: +1 952 912-3444

www.digi.com/support www.digi.com

## Contents

| Chapter 1: About the NET + 50    |    |

|----------------------------------|----|

| Introduction                     |    |

| ARM7TDMI                         |    |

| The NET+50                       |    |

| Hardware design                  |    |

| Device modules                   |    |

| Chapter 2: NET + 50 Features     | 5  |

| NET+50 chip key features         | 6  |

| Chapter 3: NET + 50 Chip Package | 9  |

| NET+50 chip pinouts              |    |

| Table Information and Tables     |    |

| System bus interface             |    |

| Chip select controller           |    |

| Ethernet interface               |    |

| MIC interface                    | 17 |

| UARTS-SPI-GPIO                   |    |

| Clock generation/system reset    | 20 |

| JTAG port for ARM core           |    |

| Power supply                     | 21 |

| Signal description summary       |    |

| System bus interface             |    |

| Chip select controller           |    |

| Ethernet MII                     |    |

- - - - iii

| MIC interface                                       | 25 |

|-----------------------------------------------------|----|

| GPIO (PORTA/B/C)                                    | 29 |

| Clock generation and reset                          | 30 |

| Test support                                        | 31 |

| ARM debugger                                        | 32 |

| Power                                               | 33 |

| Packaging                                           | 34 |

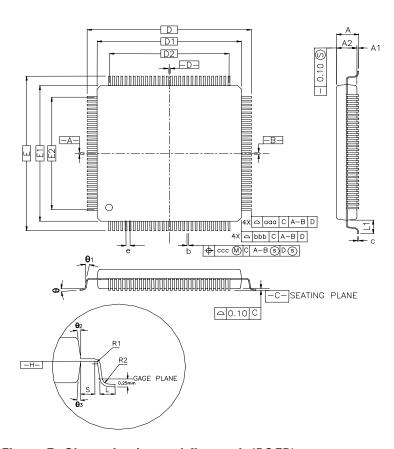

| NET+50 PQFP package                                 | 34 |

| BGA package                                         | 36 |

|                                                     |    |

| Chapter 4: Working with the CPU                     | 39 |

| Thumb concept                                       | 40 |

| Working with ARM exceptions                         | 40 |

| Exceptions                                          |    |

| Exception priorities                                | 42 |

| Exception vector table                              | 43 |

| Entering and exiting an exception (software action) | 44 |

| Exception entry / exit summary                      | 45 |

| Hardware interrupts                                 | 46 |

| Chantar E. BBus Madula                              | 40 |

| Chapter 5: BBus Module                              |    |

| BBus functionality                                  |    |

| Cycles and BBus arbitration                         |    |

| Order of arbitration                                |    |

| Address decoding                                    | 51 |

| Chapter 6: The GEN Module                           | 53 |

| Module configuration                                |    |

| GEN module hardware initialization                  |    |

| NET+50 bootstrap initialization                     |    |

| ·                                                   |    |

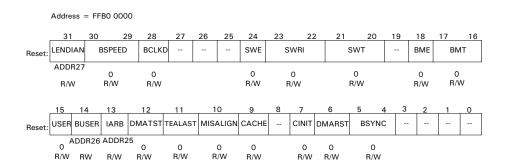

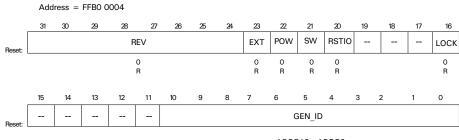

| System registers                                    |    |

| System Control register                             |    |

| System Status register                              |    |

| PLL                                                 |    |

| Timing Registers                                    | 64 |

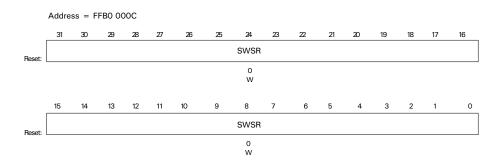

|    | Software Service register            | 65  |

|----|--------------------------------------|-----|

|    | Timer Control registers              | 65  |

|    | Timer Status register                | 67  |

|    | General Purpose I/O (GPIO) Registers | 68  |

|    | PORTA Register                       | 68  |

|    | PORTB Register                       | 73  |

|    | PORTC register                       | 79  |

|    | Interrupt generation and control     | 86  |

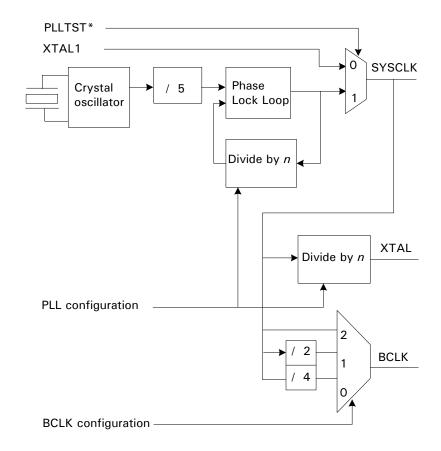

|    | NET+50 internal clock generation     | 88  |

|    | System clock generation              | 89  |

|    | Internal XTAL clock reference        | 90  |

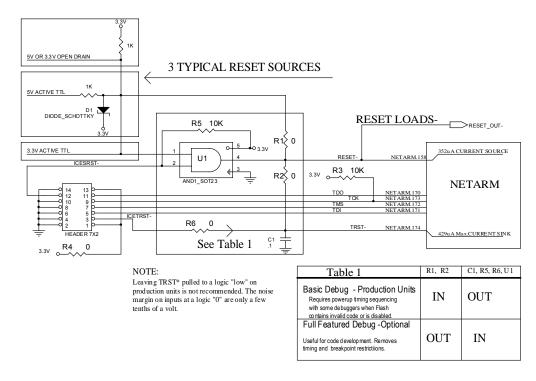

|    | Reset circuit                        | 93  |

|    | Powerup reset                        | 93  |

|    | External reset                       | 94  |

|    | Watch-Dog reset                      | 94  |

|    | ENI reset                            | 94  |

|    | Software reset                       | 94  |

|    | Reset conditions                     | 94  |

|    | PLLTest Mode                         | 95  |

|    |                                      |     |

| Ch | apter 7: Cache                       | 99  |

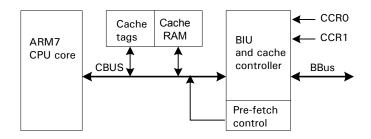

|    | CBUS and BBus system buses           | 100 |

|    | BIU and cache controller             | 100 |

|    | Cache                                | 101 |

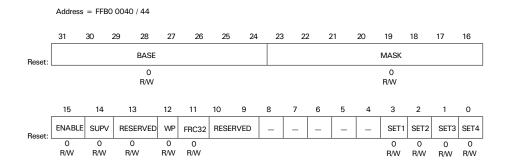

|    | Cache control registers              | 102 |

|    | Cache operation                      | 102 |

|    | Cache line fill                      | 102 |

|    | Cache line replacement               | 103 |

|    | Cache line locking                   | 103 |

|    | 32-bit pre-fetch                     | 103 |

|    | Cache initialization                 | 103 |

|    | Cache Control registers              | 104 |

|    | Register and bit definitions         | 104 |

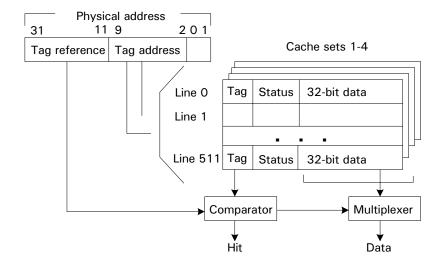

|    | Cache RAM                            | 106 |

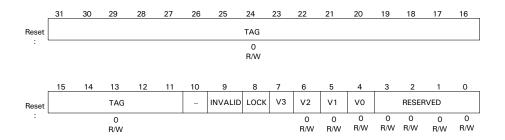

|    | Cache TAG format                     | 107 |

|    |                                      |     |

|    | Cache TAG format and definitions     | 108 |

| Chapter 8: Memory Controller Module            | 111  |

|------------------------------------------------|------|

| MEM module features                            | 112  |

| Memory control signals                         | 112  |

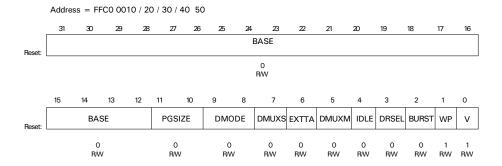

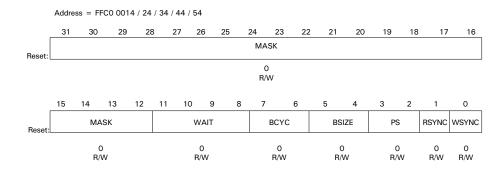

| Configuration registers                        | 113  |

| Registers                                      | 113  |

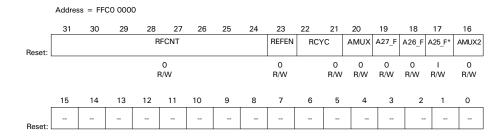

| Memory Module Control register (MMCR)          | 114  |

| Memory control signals                         | 126  |

| Data bus (D31:0)                               | 127  |

| Address bus (A27:0)                            | 127  |

| Chip selects/RAS (CSx*/RAS)                    |      |

| Setting the Chip Select address range          |      |

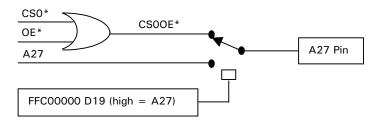

| CSO* boot configuration                        |      |

| Column address strobes (CAS)                   |      |

| Read/Write (R/W*)                              |      |

| Output enable (OE*)                            |      |

| Write enable (WE*)                             |      |

| Byte enable (BEx*)                             |      |

| Transfer Acknowledge (TA*)                     |      |

| Transfer Error Acknowledge (TEA*)              |      |

| Basic configurations                           |      |

| Static RAM                                     |      |

| Fast page and EDO DRAM                         |      |

| SDRAM                                          |      |

| NET+50 SDRAM interconnect                      |      |

| SDRAM x16 bursting considerations              |      |

| x32 SDRAM configurationx16 SDRAM configuration |      |

| _                                              |      |

| WAIT configuration                             |      |

| Burst terminate solution                       | ,159 |

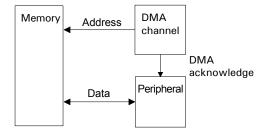

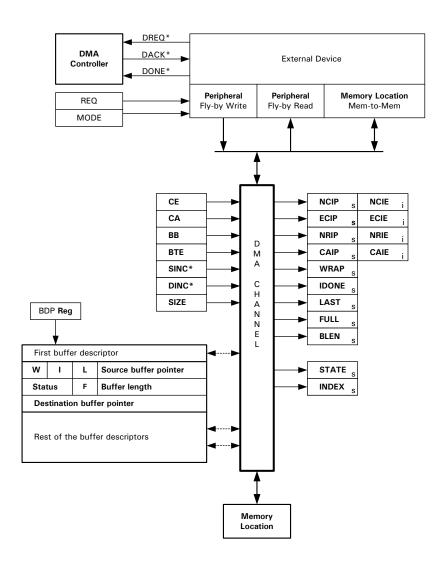

| Chapter 9: DMA Controller Module               | 163  |

| DMA transfers                                  | 164  |

| Fly-by operation                               |      |

| Memory-to-memory operation                     |      |

| DMA module                                     |      |

| DMA controller assignments                     |      |

| DMA Channel                                           | 16/   |

|-------------------------------------------------------|-------|

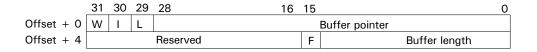

| DMA buffer descriptor                                 | 169   |

| Source buffer pointer                                 | 171   |

| Buffer length                                         | 171   |

| Destination address pointer                           | 172   |

| DMA channel configuration                             | 172   |

| DMA registers                                         |       |

| DMA buffer descriptor pointer                         |       |

| DMA Control register and bit definition               |       |

| DMA Status/Interrupt Enable register and bit definiti | on180 |

| Ethernet receiver considerations                      | 182   |

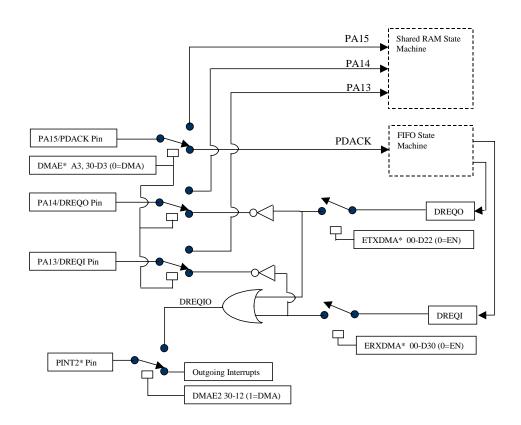

| External peripheral DMA support                       | 183   |

| Signal description                                    | 183   |

| External DMA configuration                            | 185   |

| Fly-by mode                                           | 186   |

| Memory-to-memory mode                                 | 187   |

| DMA controller reset                                  | 188   |

|                                                       |       |

| Chapter 10: Ethernet Controller Module                | 189   |

| Ethernet (EFE) front-end module                       | 190   |

| Media access controller (MAC) module                  |       |

| Ethernet controller configuration                     |       |

| Ethernet Registers                                    |       |

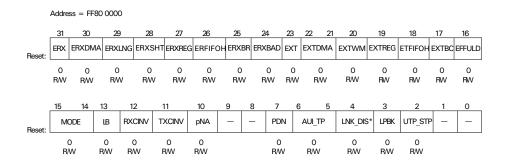

| Ethernet General Control register and bit definitions |       |

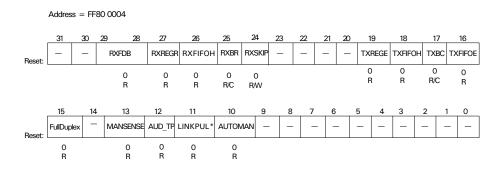

| Ethernet General Status register and bit definitions  |       |

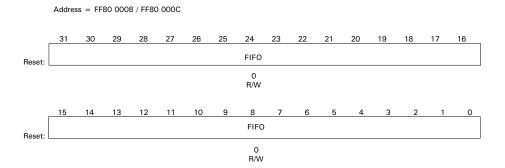

| Ethernet FIFO Data register                           |       |

| Ethernet Transmit Status register and bit definitions |       |

| Ethernet Receive Status register and bit definitions  | 208   |

| MAC registers                                         | 211   |

| MAC Configuration register and bit definitions        | 211   |

| MAC Test register and bit definitions                 | 213   |

| PCS registers                                         |       |

| PCS Configuration register and bit definitions        |       |

| PCS Test register                                     |       |

| STL registers                                         |       |

| STL Configuration register and bit definitions        |       |

|                                                       |       |

• • • • • vii

|     | STL Test register and bit definitions               | .218  |

|-----|-----------------------------------------------------|-------|

|     | Transmit Control registers                          | .219  |

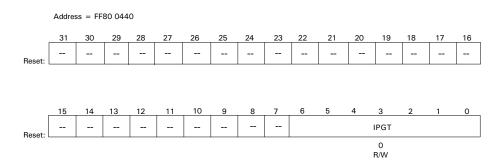

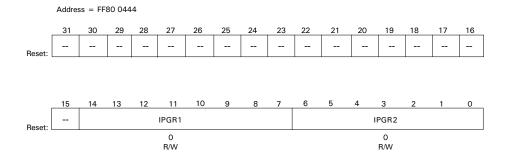

|     | Inter-Packet Gap (IPG) registers                    | .219  |

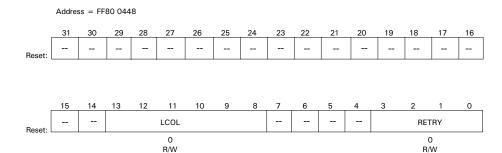

|     | Collision Window/Collision Retry register           | .225  |

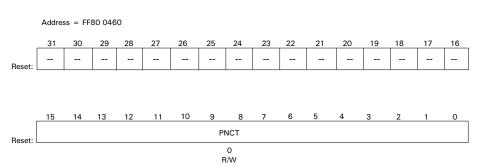

|     | "Simulation" registers                              | .226  |

|     | Receive Control registers                           | .229  |

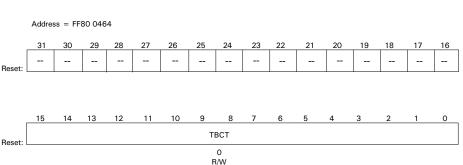

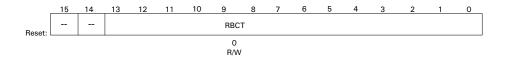

|     | Receive Byte Counter (RBCT)                         | .229  |

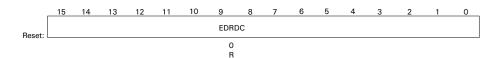

|     | Receive Counter Decodes (ECRDC)                     | .229  |

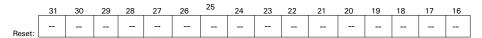

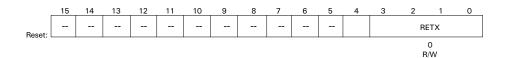

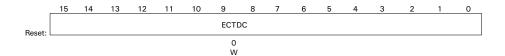

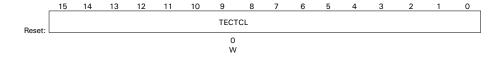

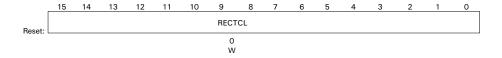

|     | Test Operate Receive Counters (RECTCL)              | .230  |

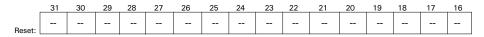

|     | PCS Control registers                               | .231  |

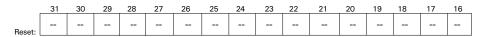

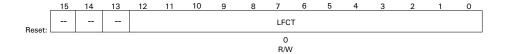

|     | Link Fail Counter (LFCT)                            | .231  |

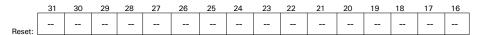

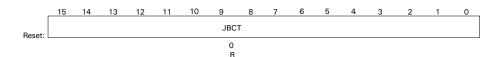

|     | 10 MB Jabber Counter (JBCT)                         | .231  |

|     | 10 MB Loss of Carrier Counter (DTLB)                | .232  |

|     | Ethernet MII interface signals                      | .233  |

|     | MII Control registers                               | .235  |

|     | MII Command register and bit definitions            | .235  |

|     | MII Address register and bit definitions            | .236  |

|     | MII Write Data register and bit definition          | .236  |

|     | MII Read Data register and bit definition           | .237  |

|     | MII Indicators register and bit definitions         | .237  |

|     | Statistics monitoring                               | .238  |

|     | Error Statistics registers                          | .239  |

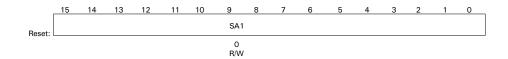

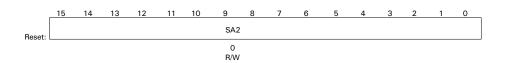

|     | Station Address registers/multicast hash table      | .241  |

|     | Station Address Filter register and bit definitions | .242  |

|     | Station Address register and bit definitions        | .243  |

|     | Multicast hash table entries and bit definitions    | .244  |

|     |                                                     |       |

| Cha | pter 11: Serial Controller Module                   | . 251 |

|     | Features                                            |       |

|     | Bit-rate generator                                  |       |

|     | Serial protocols                                    |       |

|     | UART mode                                           |       |

|     | HDLC mode                                           |       |

|     | SPI Mode                                            |       |

|     | General purpose I/O configurations                  |       |

|     |                                                     |       |

|     | Serial port performance                             | .4/1  |

Viii .....

|              | Configuration                                        | 272            |

|--------------|------------------------------------------------------|----------------|

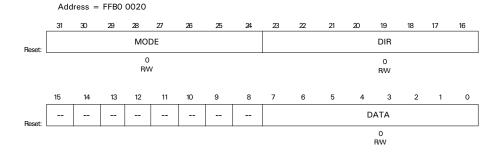

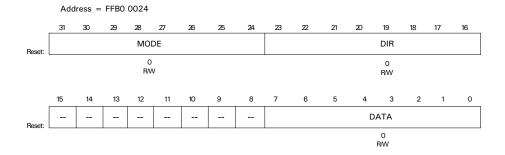

|              | Serial controller register diagrams                  | 273            |

|              | Serial Channel registers                             | 278            |

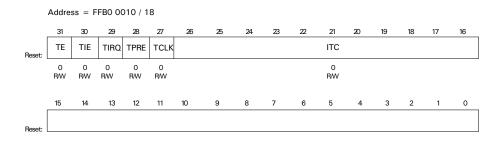

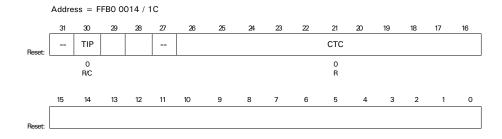

|              | Serial Channel Control Register A                    |                |

|              | Serial Channel Control Register B                    |                |

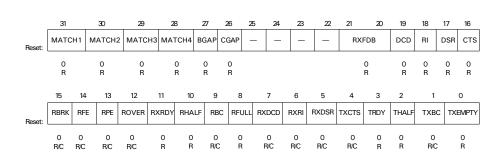

|              | Serial Channel Status Register A                     |                |

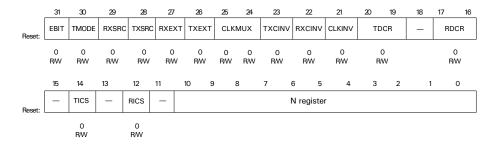

|              | Serial Channel Bit-Rate registers                    | 296            |

|              | Serial Channel FIFO registers                        | 302            |

|              | Receive Gap Timer registers                          | 302            |

|              | Receive Buffer Timer register and bit definitions    |                |

|              | Receive Character Timer register and bit definitions | 305            |

|              | Receive Match registers                              | 306            |

|              | Receive Match register and bit definitions           |                |

|              | Receive Match MASK register and bit definitions      | 307            |

|              | Control Register C (HDLC)                            | 308            |

|              | Status Register B (HDLC)                             | 309            |

|              | Status Register B and bit definitions                |                |

|              | Status Register C (HDLC)                             |                |

|              | Status Register C and bit definitions                |                |

|              | FIFO Data Register LAST (HDLC)                       |                |

|              | , ,                                                  |                |

| ٠ h          | apter 12: MIC Controller Module                      | 317            |

| <i>,</i> , , |                                                      |                |

|              | MIC controller modes of operation                    |                |

|              | MIC modes of operation                               |                |

|              | MIC module interrupts                                |                |

|              | MIC module hardware initialization                   |                |

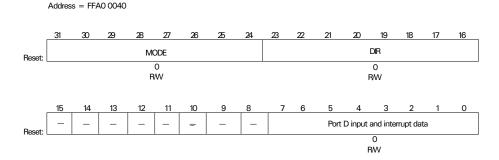

|              | GPIO mode                                            |                |

|              | GPIO function configurations                         |                |

|              | Examples using PORTF                                 |                |

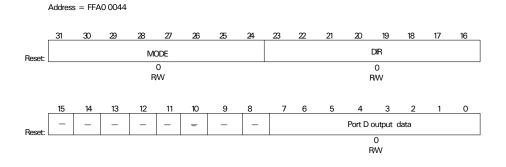

|              | PORTD register                                       |                |

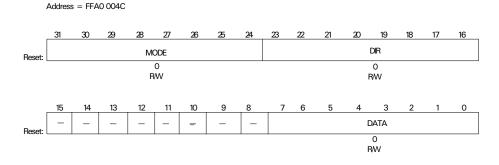

|              | PORTF register                                       |                |

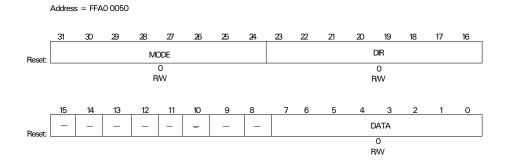

|              | PORTG register                                       |                |

|              | PORTH register                                       |                |

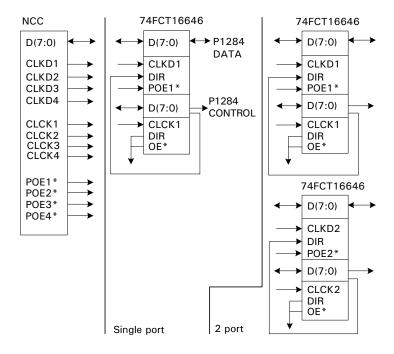

|              | IEEE 1284 host interface (4-port) module             |                |

|              | IEEE 1284 signal cross reference                     |                |

|              | ILLE 1207 Signat Closs reference                     | ·············· |

• • • • • ix

| IEEE 1284 port multiplexing                          | 342 |

|------------------------------------------------------|-----|

| IEEE 1284 mode configuration                         | 342 |

| IEEE negotiation                                     | 343 |

| IEEE 1284 forward compatibility mode                 | 343 |

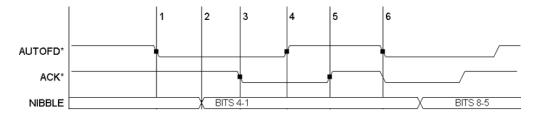

| IEEE 1284 nibble mode                                | 344 |

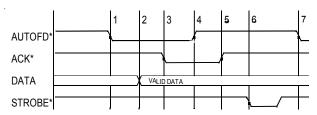

| IEEE 1284 byte mode                                  | 345 |

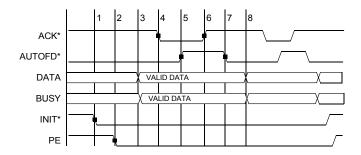

| IEEE 1284 forward ECP mode                           | 346 |

| IEEE 1284 reverse ECP mode                           | 348 |

| IEEE 1284 EPP mode                                   | 350 |

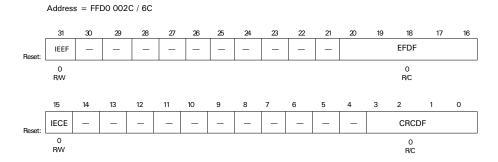

| IEEE 1284 Configuration registers                    | 354 |

| IEEE 1284 Port Control registers and bit definitions | 354 |

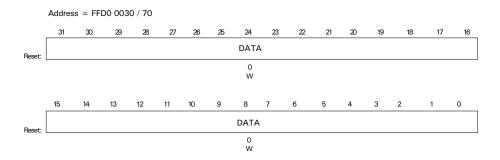

| IEEE 1284 Channel Data registers                     | 359 |

| IEEE 1284 strobe pulse width                         | 360 |

| IEEE 1284 external loopback mode                     | 361 |

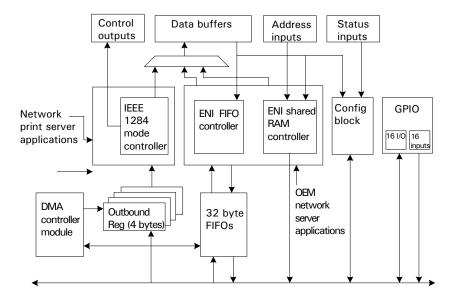

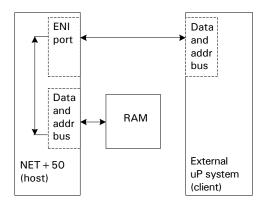

| ENI mode overview                                    | 361 |

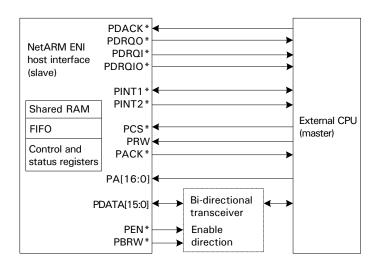

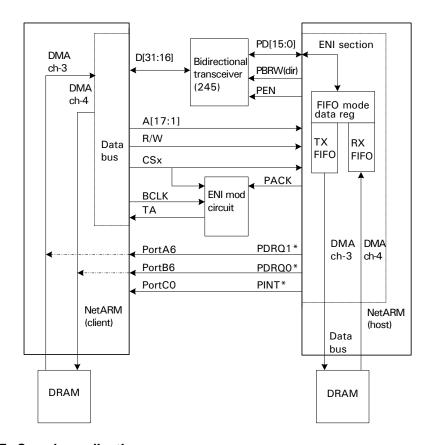

| ENI host interface                                   | 362 |

| Signal descriptions                                  | 364 |

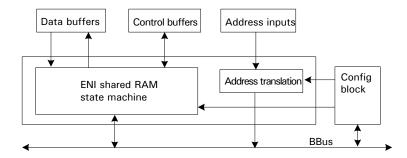

| ENI shared RAM mode                                  | 369 |

| Memory map                                           | 369 |

| Shared RAM                                           | 370 |

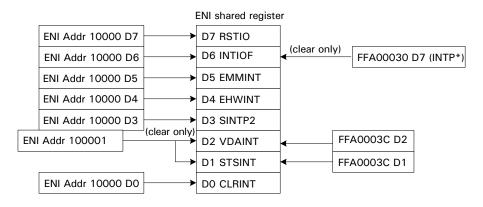

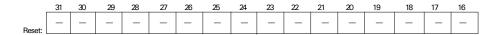

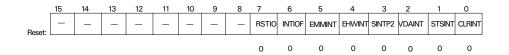

| Shared register                                      | 371 |

| Clear interrupts                                     | 376 |

| Address interrupts                                   | 376 |

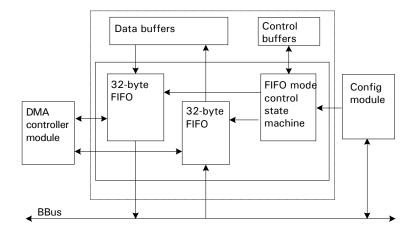

| ENI FIFO mode module                                 |     |

| FIFO Data register                                   |     |

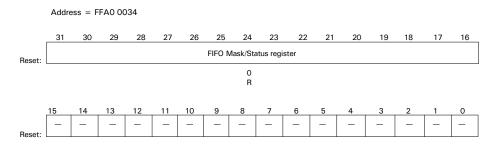

| FIFO Mask/Status register and bit definition         |     |

| ENI mode registers                                   |     |

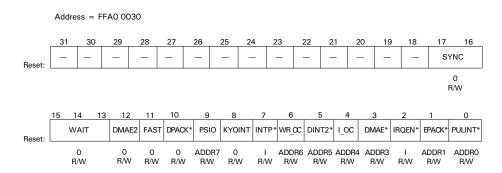

| General Control register and bit definitions         |     |

| General Status register and bit definitions          |     |

| ENI mode FIFO Data register                          |     |

| ENI Control register and bit definitions             |     |

| ENI Pulsed Interrupt register and bit definition     |     |

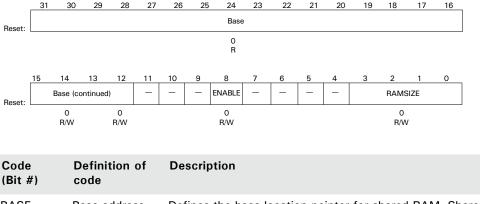

| ENI Shared RAM Address register and bit definitions  |     |

|                                                      |     |

| Chapter 13: Timing                                   | 405 |

| Thermal considerations                               | 406 |

| Absolute maximum ratings                             | 407 |

|                                                      |     |

| DC characteristics                                  | 407 |

|-----------------------------------------------------|-----|

| AC characteristics                                  | 409 |

| Output pad timing                                   | 409 |

| Clock relationships                                 | 411 |

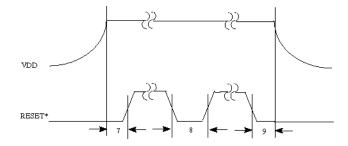

| RESET* timing                                       | 411 |

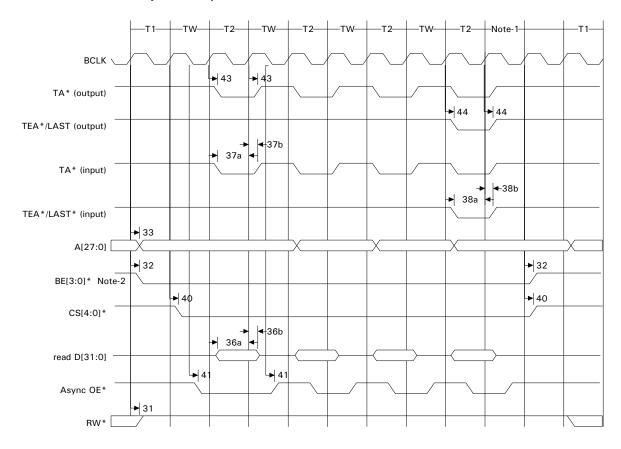

| SRAM timing                                         | 412 |

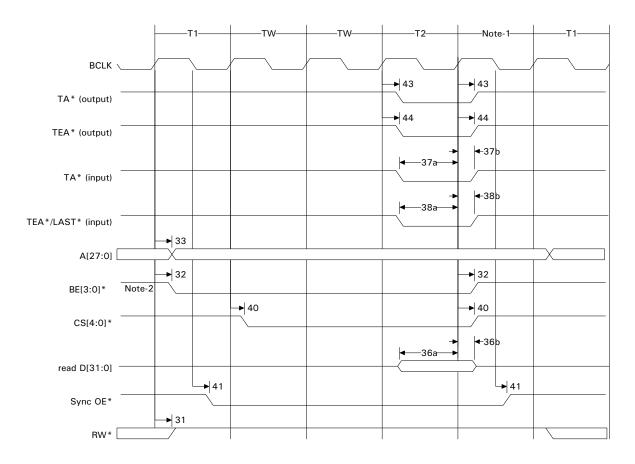

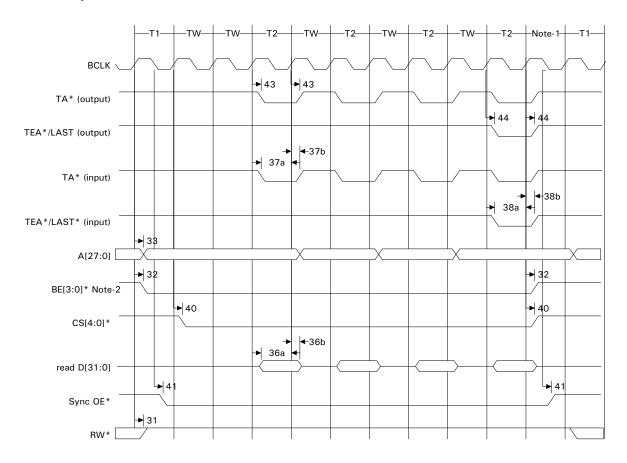

| SRAM Sync Read (WAIT = 2)                           | 413 |

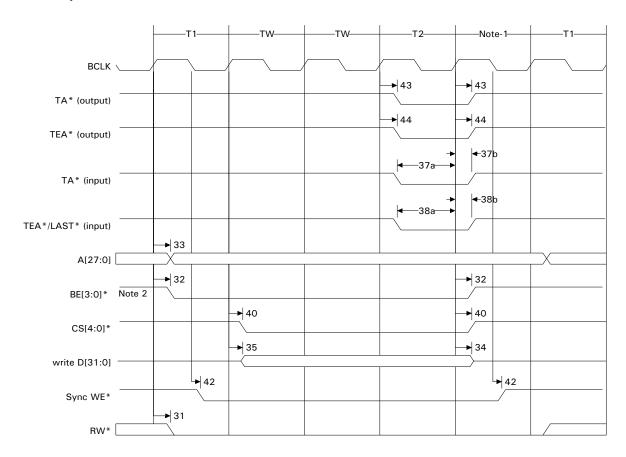

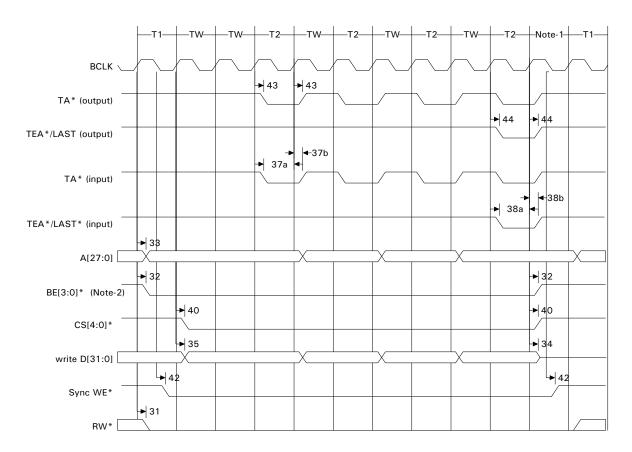

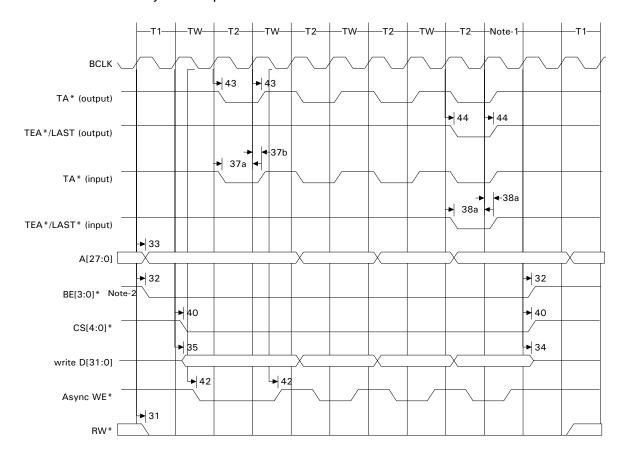

| SRAM Sync Write (WAIT = 2)                          | 414 |

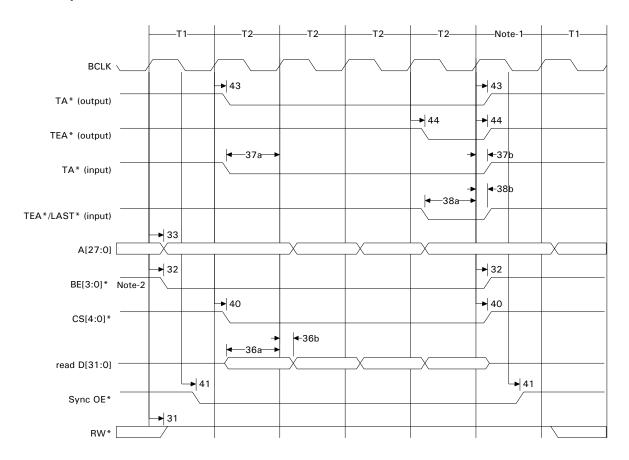

| SRAM Sync Burst Read (2-111) (WAIT = 0, BCYC = 00)  | 415 |

| SRAM Sync Burst Read (4-222) (WAIT = 2, BCYC = 01)  | 416 |

| SRAM Sync Burst Write (4-222) (WAIT = 2, BCYC = 01) | 417 |

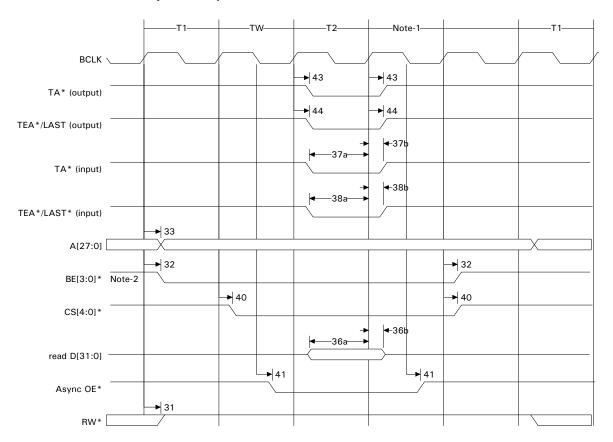

| SRAM Async Read (WAIT = 2)                          | 418 |

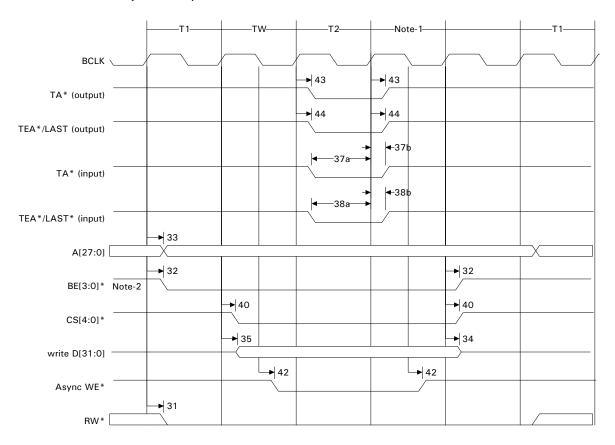

| SRAM Async Write (WAIT = 2)                         | 419 |

| SRAM Async Burst Read (WAIT = 2, BCYC = 01)         | 420 |

| SRAM Async Burst Write (WAIT = 2, BCYC = 01)        | 421 |

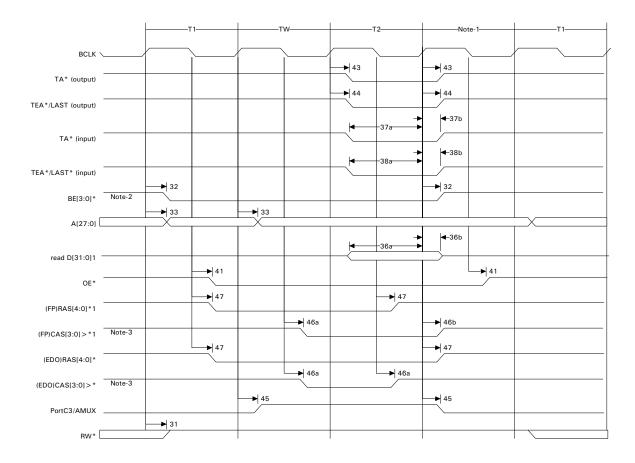

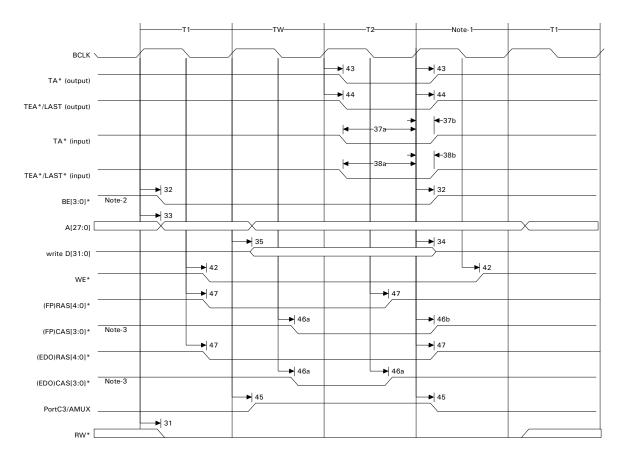

| Fast Page and EDO DRAM Timing                       | 422 |

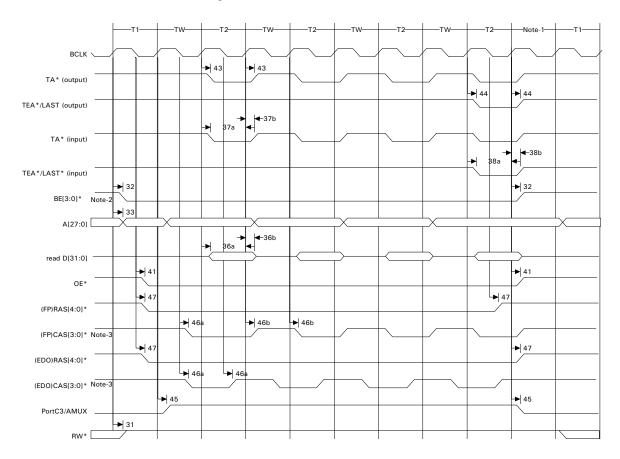

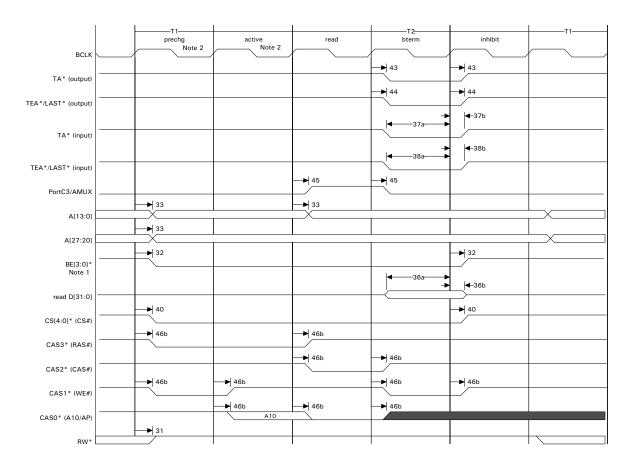

| Fast Page and EDO DRAM Read                         | 423 |

| Fast Page and EDO DRAM Write                        | 424 |

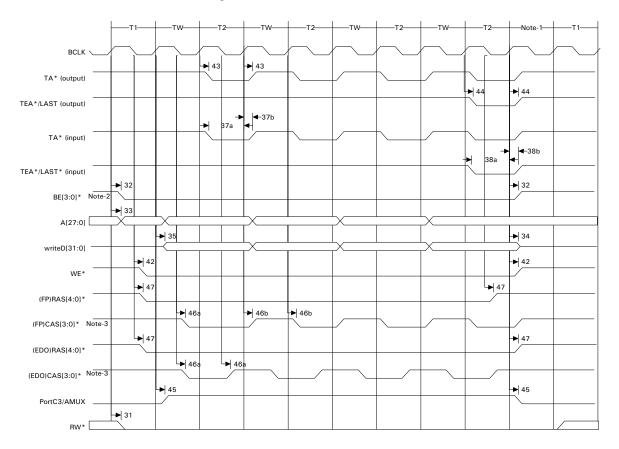

| Fast Page and EDO DRAM Burst Read                   | 425 |

| Fast Page and EDO DRAM Burst Write                  | 427 |

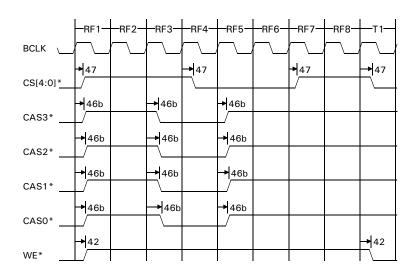

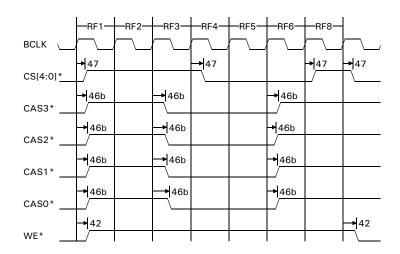

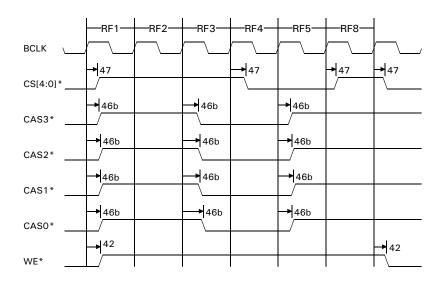

| Fast Page and EDO DRAM Refresh (RCYC = 0)           | 429 |

| Fast Page and EDO DRAM Refresh (RCYC = 1)           | 429 |

| Fast Page and EDO DRAM Refresh (RCYC = 2)           | 430 |

| Fast Page and EDO DRAM Refresh (RCYC = 3)           | 430 |

| SDRAM timing                                        | 431 |

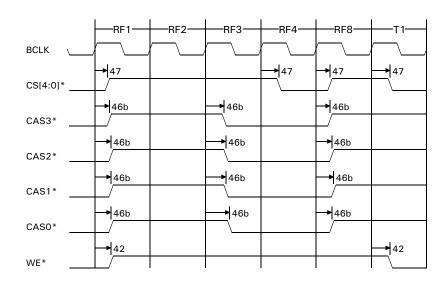

| SDRAM Read (CAS Latency = 1)                        | 432 |

| SDRAM Read (CAS Latency = 2)                        | 433 |

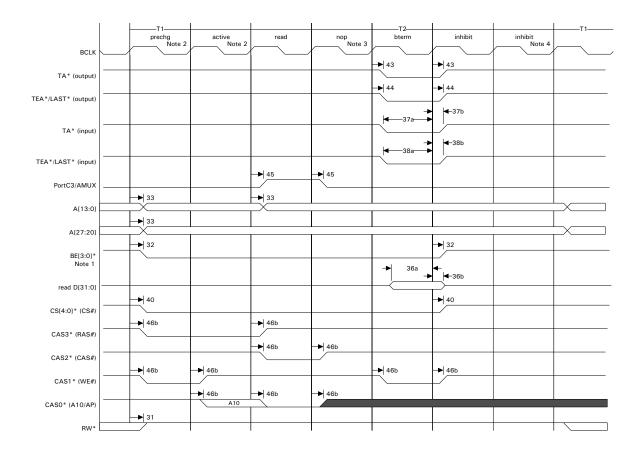

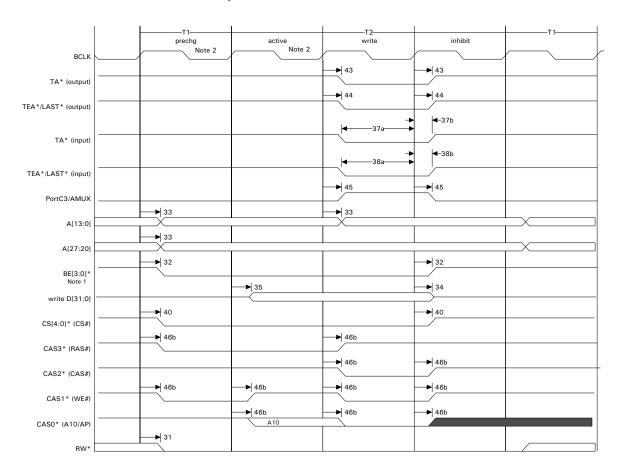

| SDRAM Write (CAS Latency = 2)                       | 434 |

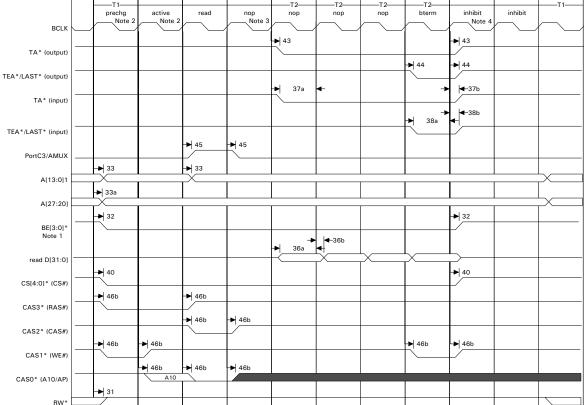

| SDRAM Burst Read (CAS Latency = 1)                  | 435 |

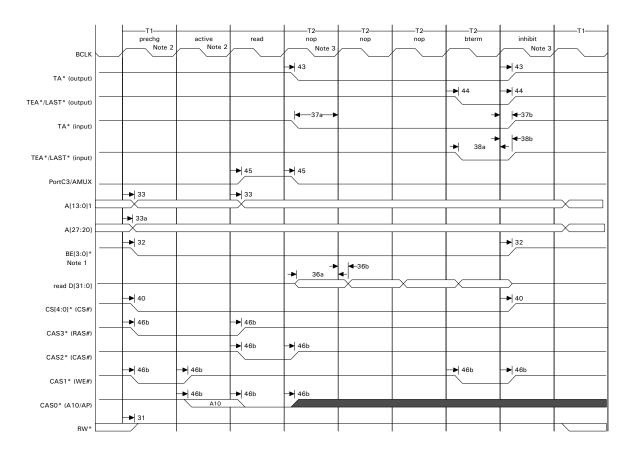

| SDRAM Burst Read (CAS Latency = 2)                  | 436 |

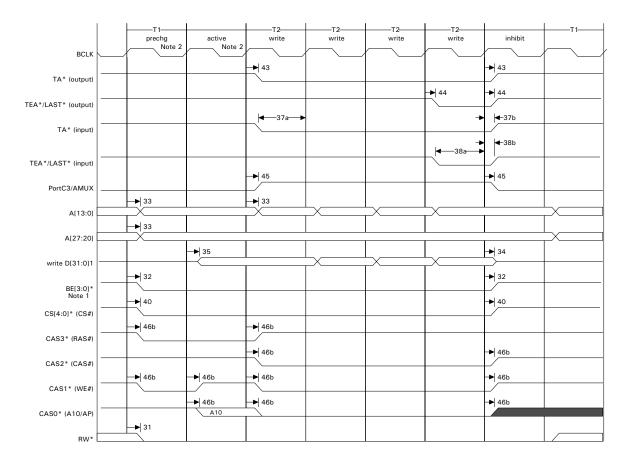

| SDRAM Burst Write (CAS Latency = 2)                 | 437 |

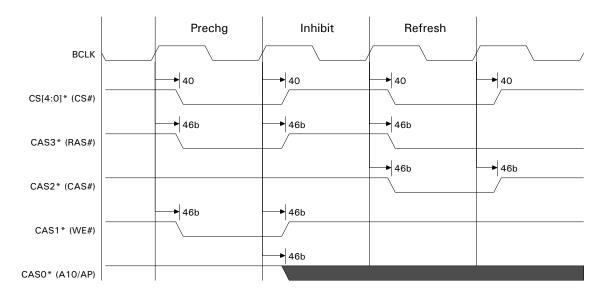

| SDRAM Refresh Command                               | 438 |

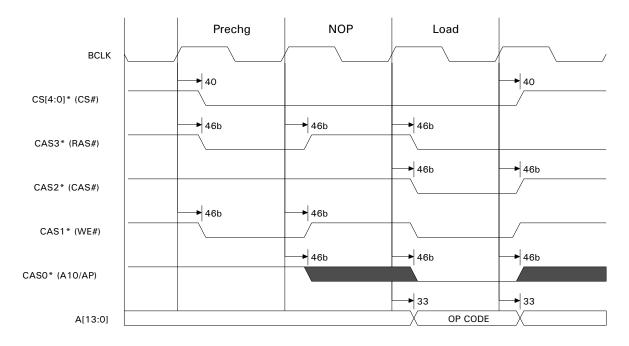

| SDRAM Load-Mode Command                             | 439 |

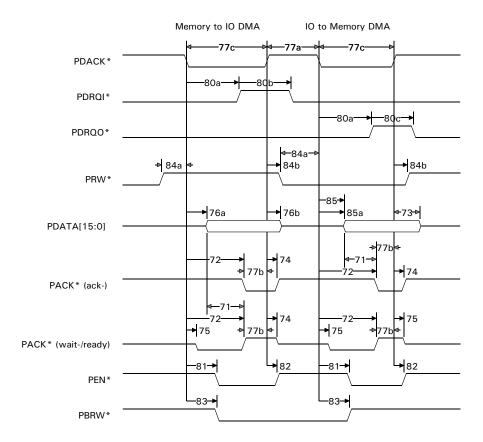

| External DMA timing                                 | 440 |

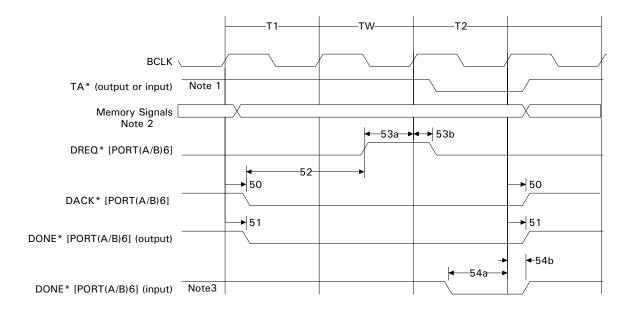

| External Fly-by DMA                                 | 441 |

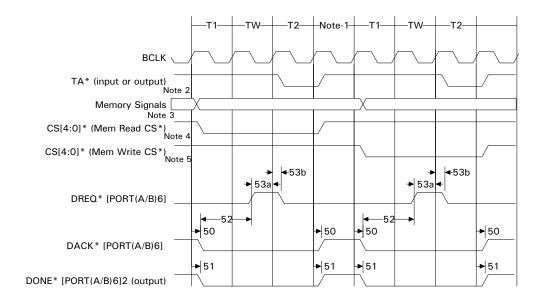

| External Memory-to-Memory DMA                       |     |

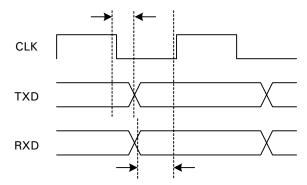

| SPI timing                                          | 445 |

|                                                     |     |

.... xi

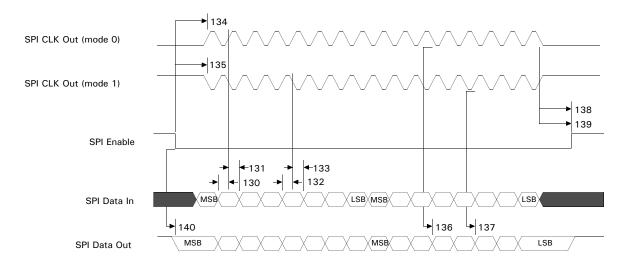

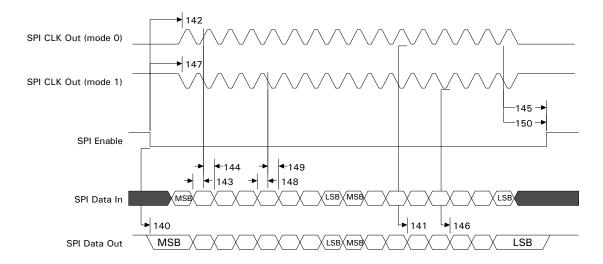

| SPI Master mode 0 and 1 (two-byte transfer) | 445  |

|---------------------------------------------|------|

| SPI Slave mode 0 and 1                      | 446  |

| MIC timing                                  | 448  |

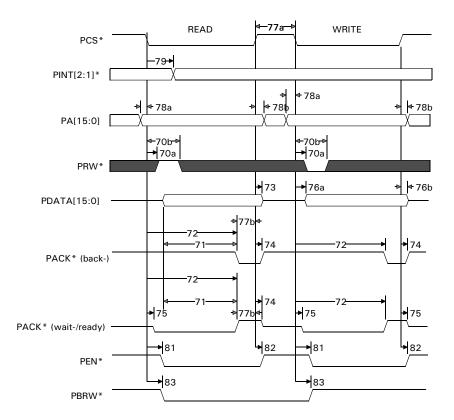

| ENI Shared RAM and Register Cycle timing    | 450  |

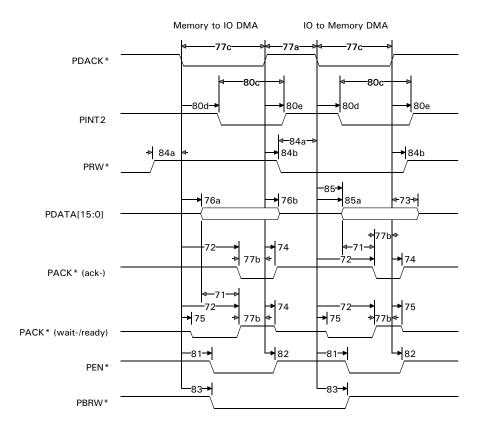

| ENI Single Direction DMA timing             | 451  |

| ENI Dual Direction DMA timing               | 452  |

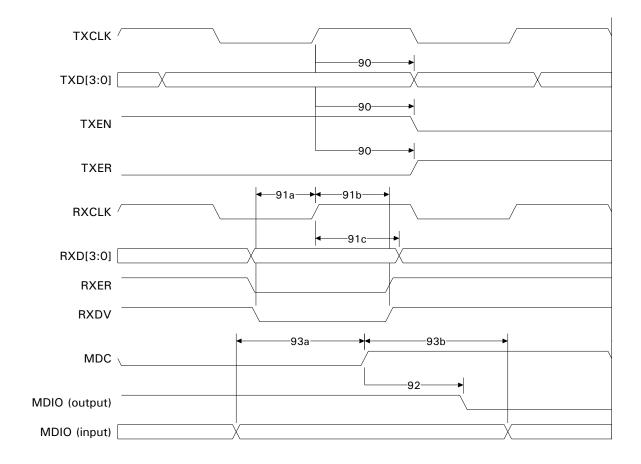

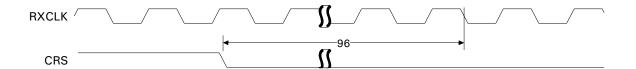

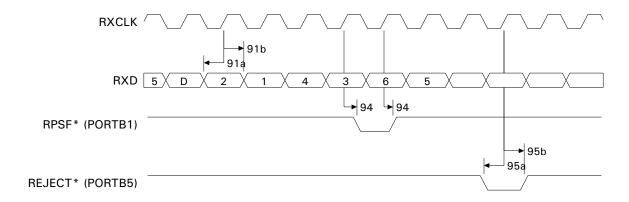

| Ethernet timing                             | 453  |

| Ethernet timing diagram                     | 454  |

| Ethernet Receive Clock Idle                 | 454  |

| External Ethernet CAM Filtering             | 455  |

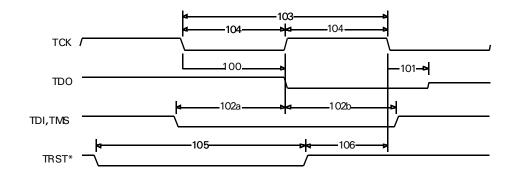

| JTAG timing                                 | 455  |

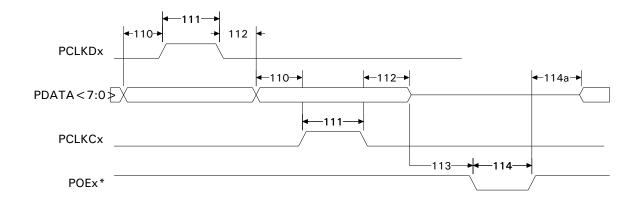

| 1284 Port Multiplexing timing               | 456  |

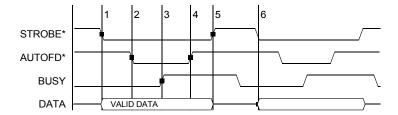

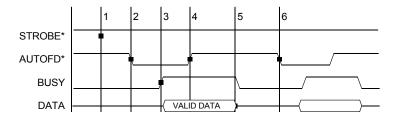

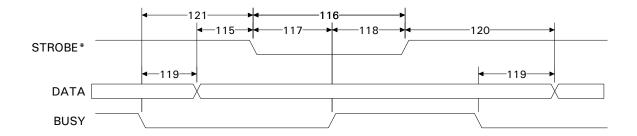

| 1284 Compatibility mode timing              | 457  |

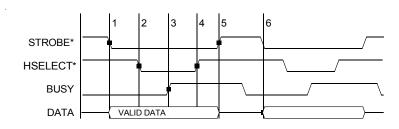

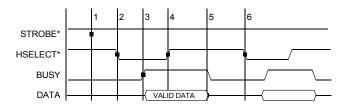

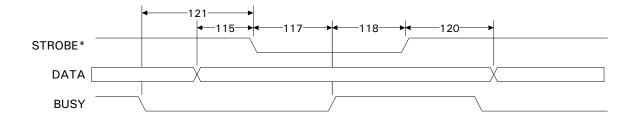

| Forward ECP mode timing                     | 459  |

| Crystal oscillator specifications           | 460  |

| Appendix A: ARM Exceptions                  | 461  |

| About ARM exceptions                        | 462  |

| Reset exception                             | 462  |

| Undefined exception                         | 462  |

| SWI exception                               | 463  |

| Abort exception                             | 463  |

| IRQ exception                               | 464  |

| FIDO exception                              | 47.4 |

Index

# Using This Guide

Review this section for basic information about the guide you are using, as well as general support and contact information.

## About this guide

This guide provides information about the Digi NET+50 32-bit networked microprocessor. The NET+50 are part of the Digi NET+ARM line of SoC (Systemon-Chip) products, and support any type of high-bandwidth applications in Intelligent Networked Devices.

The NET+ARM chip is part of the NET+Works integrated product family, which includes the NET+OS network software suite.

## Who should read this guide

This guide is for hardware developers, system software developers, and applications programmers who want to use the NET+50 for development.

To complete the tasks described in this guide, you must:

- Understand the basics of hardware and software design, operating systems, and microprocessor design.

- Understand the NET+50 architecture.

## What's in this guide

This table shows where you can find specific information in this guide:

| To read about                                                                                 | See                                      |

|-----------------------------------------------------------------------------------------------|------------------------------------------|

| The NET + 50 chip                                                                             | Chapter 1, "About the NET + 50"          |

| NET + 50 key features                                                                         | Chapter 2, "NET + 50 Features"           |

| NET + 50 PQFP/BGA pin/ball grid array assignments and packaging                               | Chapter 3, "NET + 50 Chip Package"       |

| NET+50 CPU and the ARM <i>Thumb</i> concept                                                   | Chapter 4, "Working with the CPU"        |

| BBus functionality                                                                            | Chapter 5, "BBus Module"                 |

| General (GEN) module functionality                                                            | Chapter 6, "The GEN Module"              |

| ARM7TDMI stand-alone core and instruction/data cache, write protection, and pre-fetch control | Chapter 7, "Cache"                       |

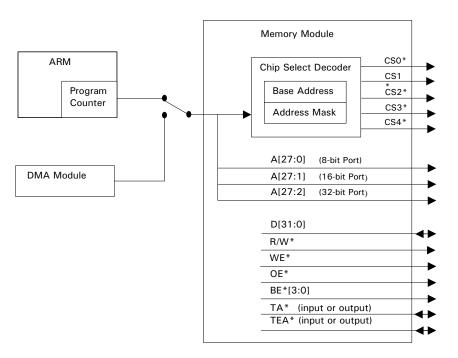

| How the NET + 50 can be configured to interface with different types of memory devices        | Chapter 8, "Memory Controller Module"    |

| DMA controller, supported DMA channels, and internal and externalDMA transfers                | Chapter 9, "DMA Controller Module"       |

| Ethernet controller module                                                                    | Chapter 10, "Ethernet Controller Module" |

| Serial channel A and serial channel B                                                         | Chapter 11, "Serial Controller Module"   |

| Multi interface controller (MIC)                                                              | Chapter 12, "MIC Controller Module"      |

| NET + 50 timing information and diagrams                                                      | Chapter 13, "Timing"                     |

| ARM exceptions                                                                                | Appendix A, "ARM Exceptions"             |

## Conventions used in this guide

This table describes the typographic conventions used in this guide:

| This convention | Is used for                                          |  |  |  |  |  |  |

|-----------------|------------------------------------------------------|--|--|--|--|--|--|

| italic type     | Emphasis, new terms, variables, and document titles. |  |  |  |  |  |  |

| monospaced type | Filenames, pathnames, and code examples.             |  |  |  |  |  |  |

#### Related documentation

- NET+50/20M Jumpers and Components provides a hardware description of the NET+Works Development Board, and includes information about jumpers, connectors, switches, and interface configuration as well as development board diagrams.

- Review the documentation CD-ROM that came with your development kit for information on third-party products and other components.

- Refer to the NET+OS software documentation for information appropriate to the chip you are using.

## **Documentation updates**

Digi occasionally provides documentation updates on the Web site (www.digi.com/support).

Be aware that if you see differences between the documentation you received in your package and the documentation on the Web site, the Web site content is the latest version.

## **Customer support**

To get help with a question or technical problem with this product, or to make comments and recommendations about our products or documentation, use the contact information listed in this table:

| For               | Contact information                                                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------|

| Technical support | United States: +1 877 912-3444<br>Other locations: +1 952 912-3444<br>www.digi.com/support<br>www.digi.com |

## *About the NET+50*

CHAPTER 1

T he Digi NET+50 is a system-on-a-chip ASIC designed for use in intelligent network devices and Internet appliances. The NET+50 consists of a 208 plastic-quad-flat-pack (PQFP) package and a 208 ball-grid-array (BGA) package. The NET+50 is a high-performance, highly-integrated 32-bit chip.

. . . . . . .

#### Introduction

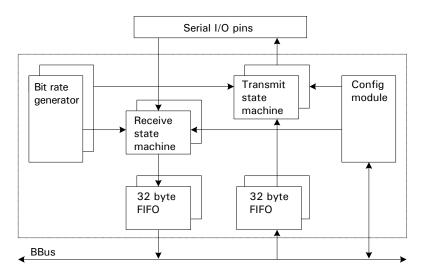

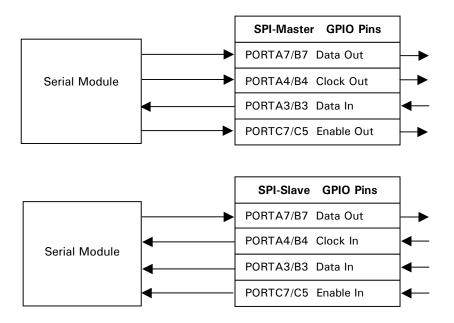

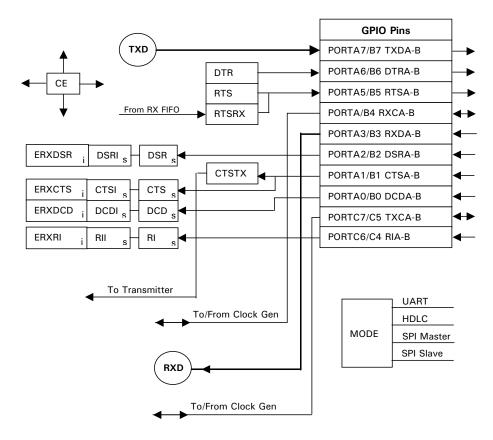

The NET+50 supports almost any networking scenario, with a 10/100 BaseT Ethernet MAC with MII interface and two independent serial ports, each of which can run in UART, HDLC, or SPI modes. The CPU is an ARM7TDMI 32-bit RISC processor core with a rich complement of support peripherals, including memory controllers for various types of memory (including flash, SDRAM, and EEPROM), programmable timers, and a 10-channel DMA controller.

The NET+50 provides all tools required for any embedded networking application.

#### ARM7TDMI

The heart of the NET+50 hardware is provided by the ARM7TDMI. The ARM7TDMI is a member of the ARM Ltd. family of general purpose 32-bit microprocessors, which offer high-performance while maintaining very low power-consumption and size.

The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles. Compared with Complex Instruction Set Computers (CISC) architecture, the RISC instruction set, and related decoding and execution mechanisms, is simpler and more streamlined. This simplicity results in a high instruction throughput and impressive real-time interrupt response, as well as a small, cost-effective circuit. The RISC architecture is conducive to pipelining, which allows the instruction fetch, decode, and execution units to operate simultaneously.

## The NET + 50

The NET+50 can be used in any embedded environment requiring networking services in an Ethernet LAN. The NET+50 contains an ARM RISC processor, 10/100 Ethernet MAC, serial ports, IEEE 1284 parallel ports, memory controllers, and parallel I/O. The NET+50 chip can interface with another processor using a RAM or shared RAM interface.

### Hardware design

The NET+50 can attach to another processor using the 1284, ENI shared RAM, or ENI FIFO interfaces. Application-specific hardware can be attached to the NET+50 system bus for custom applications that use the NET+50 internal RISC processor.

#### **Device modules**

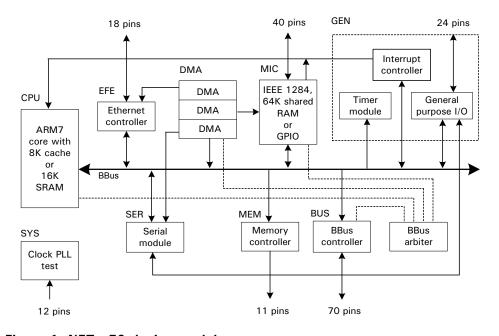

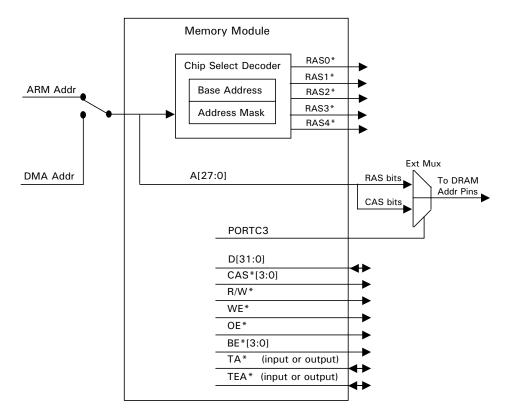

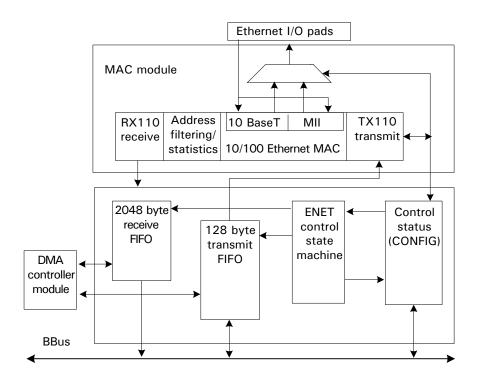

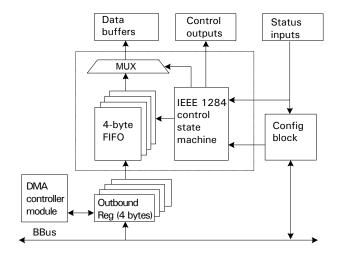

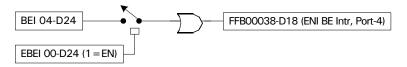

Figure 1 is an overview of the modules that make up the NET+50 device.

Figure 1: NET + 50 device modules

## NET+50 Features

CHAPTER 2

$T^{\rm he\ NET+50\ is\ based\ on\ the\ standard\ architecture\ in\ the\ NET+ARM\ family\ of\ devices.\ NET+ARM\ is\ the\ hardware\ foundation\ for\ the\ NET+Works\ family\ of\ integrated\ hardware\ and\ software\ solutions\ for\ device\ networking.}$

This chapter lists the features supported and provided by the NET+50.

. . . . . . .

5

## NET + 50 chip key features

The NET+50 chip key features include these components:

#### **CPU** core

- Full 32-bit ARM7TDMI RISC processor

- 32-bit internal bus

- 16-bit Thumb mode

- 8 Kbyte cache, configurable as 16 Kbyte RAM

- 15 general-purpose 32-bit registers

- 32-bit program counter and status register

- 5 supervisor modes, 1 user mode

- 2 programmable timers

- 2 async serial ports

#### **Bus interface**

- Five independent programmable chip selects with 256 Mbyte addressing per chip select

- 0-15 wait states per chip select

- 8-bit, 16-bit, and 32-bit peripheral support

- Normal and burst cycle support

- Glueless interface with all chip selects to SRAM, FP/EDO DRAM, SDRAM, and devices such as flash and EEPROM with SRAM interfaces

- External address decoding and cycle termination support

- Dynamic bus sizing support

- ASYNC and SYNC peripheral timing support

- Internal DRAM address multiplexing

- Internal refresh controller (CAS before RAS)

- Bootstrap support

- Internal bus arbiter support

- Configurable Endian support

#### Integrated 10/100 Ethernet MAC

- 10/100 MII-based interface to PHY

- 10 Mbit ENDEC interface

- TP-PMD and fiber-PMD device support

- Full-duplex and half-duplex modes

- Optional 4B/5B coding

- Full statistics gathering (SNMP and RMON)

- Station, broadcast, and multicast address detection and filtering

- 128 byte transmit FIFO, 2 Kbyte receive FIFO

- Intelligent receive-side buffer selection

#### P1284/MIC interface

- IEEE 1284 host interface with four parallel ports

- DMA support

- GPIO mode interface

- 64K shared RAM ENI interface (8- or 16-bit)

- Full-duplex FIFO mode interface (8- or 16-bit), including 32 byte transmit/ receive mode FIFOs

#### 10-channel DMA controller

- Two channels dedicated to Ethernet transmit and receive

- Four channels dedicated to serial transmit and receive

- Four channels dedicated to P1284/MIC interface

- Flexible buffer management

- Fly-by and memory-to-memory support

#### Serial ports

- Two fully-independent serial ports (UART, HDLC, SPI)

- Digital phase lock loop (DPLL) for receive clock extractions

- 32 byte transmit/receive FIFOs

- Internal programmable bit-rate generators

- Bit rates from 75 to 230400 in 16X mode

Bit rates from 1200 to 4 Mbps in 1X mode

(**Note:** Higher rates may be possible, depending on your design; consult factory for more information.)

- Odd, even, or no parity

- 5, 6, 7, or 8 bits; 1 or 2 stop bits

- Internal and external clock support

- Receive side character and buffer gap timers

- Four receive side data match detectors

#### **Programmable Timers**

- Two independent programmable timers (2µs to 20.7 Hours)

- Watch-dog timer (interrupt or reset on expiration)

- Bus timer

#### General-purpose I/O

- 40 programmable I/O interface pins and 16 input-only interface pins

- 36 pins with programmable interrupt

#### Clock generator

- Only a simple external crystal required

- Programmable phase lock loop (PLL), which generates a 44MHz operating frequency from an 18.432 MHz crystal. Allows a range of frequencies from 25-44 MHz, only by using external crystals.

- Direct external clock input support

#### Power and operating voltage

- $\blacksquare$  552 mW maximum (typically 368 mW), outputs switching,  $V_{DD}$  max and  $V_{CC}$  max

- 3.3 volts I/O

- 2.5 volts Core

# NET+50 Chip Package

CHAPTER 3

The NET+50 chip can be used in any embedded environment requiring networking services in an Ethernet LAN. The NET+50 chip contains an integrated ARM RISC processor, 10/100 Ethernet MAC, serial ports, IEEE 1284 parallel ports, memory controllers, and parallel I/O. The NET+50 chip can interface with another processor using a register or shared RAM interface. The NET+50 chip provides all the tools required for any embedded networking application.

. . . . . . .

## **NET + 50** chip pinouts

There are two variations of the NET+50 chip:

■ PQFP: Plastic Quad Flat Pack

■ BGA: Ball Grid Array

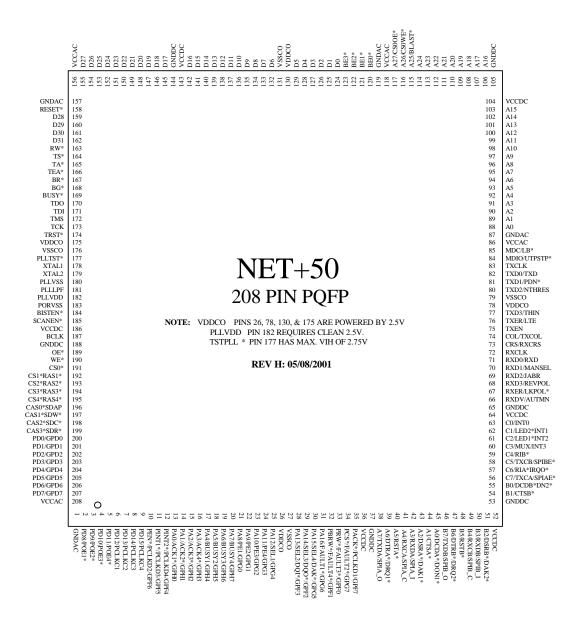

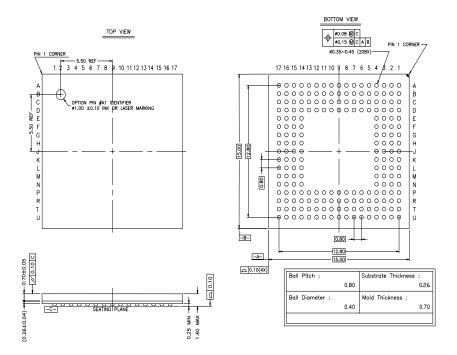

Figure 2 shows the NET+50 PQFP pinout. Figure 3 shows the BGA pinout. Table 1 through Table 8 provide the details for both pinouts.

Figure 2: NET + 50 PQFP pinout

|    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   | Pin 1 corner |

|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------------|

| 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |              |

|    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |              |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Q | Α            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | В            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | С            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | E            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | F            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | G            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | Н            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | J            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | K            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | L            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | М            |

| 0  | 0  | 0  | 0  |    |    |    |    |   |   |   |   |   | 0 | 0 | 0 | 0 | N            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Р            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | R            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | T            |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | U            |

Figure 3: NET + 50 BGA pinout

#### Table Information and Tables

Table 1 through Table 8 identify and describe the pin number assignments and ball number assignments contained in the NET+50 PQFP and BGA chips. Each table pertains to an interface, and contains the following information:

- **Signal column.** Identifies the pin name for each I/O signal. Some signals have multiple modes and are identified accordingly. You configure the mode through firmware using a configuration register. Some modes may require hardware configuration during a RESET condition.

- 208 QFP (PQFP) column. Identifies the pin number assignment for a specific I/O signal. A dagger (†) next to the pin number indicates that the pin is an input current source.

- BGA column. Identifies the ball number assignment for a specific I/O signal.

A dagger (†) next to the pin number indicates that the pin is an input current source.

- I/O column. Indicates whether the signal is input (I), output (O), or both (I/O).

- **OD (Drive) column.** Indicates the drive strength of an output buffer. The NET+50 chip uses one of three driver types:

- 2mA

- 4mA

- 8mA

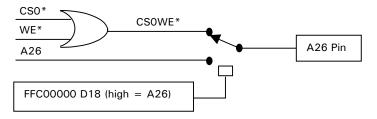

## System bus interface

| Signal |        | PQFP | BGA | I/O | OD | Description           |

|--------|--------|------|-----|-----|----|-----------------------|

| BCLK   |        | 187  | T10 | 0   | 8  | Synchronous bus clock |

| ADDR27 | CS00E* | 117† | F4† | I/O | 4  | Address bus           |

| ADDR26 | CS0WE* | 116† | F3† | I/O | 4  |                       |

| ADDR25 | BLAST* | 115† | E2† | I/O | 4  |                       |

| ADDR24 |        | 114† | D2† | I/O | 4  |                       |

| ADDR23 |        | 113† | E3† | I/O | 4  |                       |

| ADDR22 |        | 112† | E4† | I/O | 4  |                       |

| ADDR21 |        | 111† | D1† | I/O | 4  |                       |

| ADDR20 |        | 110† | C2† | I/O | 4  |                       |

| ADDR19 |        | 109† | D3† | I/O | 4  |                       |

| ADDR18 |        | 108† | C1† | I/O | 4  |                       |

| ADDR17 |        | 107† | B1† | I/O | 4  |                       |

| ADDR16 |        | 106† | B2† | I/O | 4  |                       |

| ADDR15 |        | 103† | В3† | I/O | 4  |                       |

| ADDR14 |        | 102† | A3† | I/O | 4  |                       |

| ADDR13 |        | 101† | A4† | I/O | 4  |                       |

| ADDR12 |        | 100† | B4† | I/O | 4  |                       |

| ADDR11 |        | 99†  | C3† | I/O | 4  |                       |

| ADDR10 |        | 98†  | A5† | I/O | 4  |                       |

Table 1: NET+50 PQFP/BGA Chip Pinout - System bus interface

| Signal | PQFP | BGA | I/O | OD | Description |

|--------|------|-----|-----|----|-------------|

| ADDR9  | 97†  | D4† | I/O | 4  |             |

| ADDR8  | 96†  | C4† | I/O | 4  |             |

| ADDR7  | 95†  | B5† | I/O | 4  |             |

| ADDR6  | 94†  | A6† | I/O | 4  |             |

| ADDR5  | 93†  | D5† | I/O | 4  |             |

| ADDR4  | 92†  | C5† | I/O | 4  |             |

| ADDR3  | 91†  | B6† | I/O | 4  |             |

| ADDR2  | 90†  | A7† | I/O | 4  |             |

| ADDR1  | 89†  | D6† | I/O | 4  |             |

| ADDR0  | 88†  | C6† | I/O | 4  |             |

| DATA31 | 162  | Т3  | I/O | 4  | Data bus    |

| DATA30 | 161  | R4  | I/O | 4  |             |

| DATA29 | 160  | U3  | I/O | 4  |             |

| DATA28 | 159  | U2  | I/O | 4  |             |

| DATA27 | 155  | R2  | I/O | 4  |             |

| DATA26 | 154  | R1  | I/O | 4  |             |

| DATA25 | 153  | P1  | I/O | 4  |             |

| DATA24 | 152  | P2  | I/O | 4  |             |

| DATA23 | 151  | R3  | I/O | 4  |             |

| DATA22 | 150  | N1  | I/O | 4  |             |

| DATA21 | 149  | P4  | I/O | 4  |             |

| DATA20 | 148  | Р3  | I/O | 4  |             |

| DATA19 | 147  | N2  | I/O | 4  |             |

| DATA18 | 146  | M1  | I/O | 4  |             |

| DATA17 | 145  | N4  | I/O | 4  |             |

| DATA16 | 142  | L1  | I/O | 4  |             |

| DATA15 | 141  | M4  | I/O | 4  |             |

Table 1: NET+50 PQFP/BGA Chip Pinout - System bus interface

| Signal | PQFP       | BGA | I/O | OD | Description                     |  |  |  |  |

|--------|------------|-----|-----|----|---------------------------------|--|--|--|--|

| DATA14 | 140        | МЗ  | I/O | 4  |                                 |  |  |  |  |

| DATA13 | 139        | L2  | I/O | 4  |                                 |  |  |  |  |

| DATA12 | 138        | K1  | I/O | 4  |                                 |  |  |  |  |

| DATA11 | 137        | L4  | I/O | 4  |                                 |  |  |  |  |

| DATA10 | 136        | L3  | I/O | 4  |                                 |  |  |  |  |

| DATA9  | 135        | K2  | I/O | 4  |                                 |  |  |  |  |

| DATA8  | 134        | J1  | I/O | 4  |                                 |  |  |  |  |

| DATA7  | 133        | K4  | I/O | 4  |                                 |  |  |  |  |

| DATA6  | 132        | К3  | I/O | 4  |                                 |  |  |  |  |

| DATA5  | 129        | J4  | I/O | 4  |                                 |  |  |  |  |

| DATA4  | 128        | J3  | I/O | 4  |                                 |  |  |  |  |

| DATA3  | 127        | H2  | I/O | 4  |                                 |  |  |  |  |

| DATA2  | 126        | G1  | I/O | 4  |                                 |  |  |  |  |

| DATA1  | 125        | H4  | I/O | 4  |                                 |  |  |  |  |

| DATA0  | 124        | Н3  | I/O | 4  |                                 |  |  |  |  |

| TS*    | NO CONNE   | СТ  | •   |    |                                 |  |  |  |  |

| BE3*   | 123        | G2  | I/O | 2  | Byte enable D31:D24             |  |  |  |  |

| BE2*   | 122        | F1  | I/O | 2  | Byte enable D23:D16             |  |  |  |  |

| BE1*   | 121        | G4  | I/O | 2  | Byte enable D15:D08             |  |  |  |  |

| BEO*   | 120        | G3  | I/O | 2  | Byte enable D07:D00             |  |  |  |  |

| RW*    | 163        | U4  | I/O | 2  | Transfer direction              |  |  |  |  |

| TA*    | 165†       | R5† | I/O | 8  | Data transfer acknowledge       |  |  |  |  |

| TEA*   | 166†       | T4† | I/O | 8  | Transfer error/Last acknowledge |  |  |  |  |

| BR*    | NO CONNECT |     |     |    |                                 |  |  |  |  |

| BG*    | NO CONNECT |     |     |    |                                 |  |  |  |  |

| BUSY*  | NO CONNECT |     |     |    |                                 |  |  |  |  |

Table 1: NET + 50 PQFP/BGA Chip Pinout - System bus interface

## Chip select controller

| Signal       | PQFP | BGA | I/O | OD | Description                             |

|--------------|------|-----|-----|----|-----------------------------------------|

| CS0*         | 191  | T11 | 0   | 4  | Chip select (Boot select)               |

| CS1*/RAS1*   | 192  | R12 | 0   | 4  | Chip select/DRAM RAS*                   |

| CS2*/RAS2*   | 193  | P12 | 0   | 4  | Chip select/DRAM RAS*                   |

| CS3*/RAS3*   | 194  | U11 | 0   | 4  | Chip select/DRAM RAS*                   |

| CS4*/RAS4*   | 195  | T12 | 0   | 4  | Chip select/DRAM RAS*                   |

| CAS3*/SDRAS* | 199  | T13 | 0   | 4  | DRAM column strobe D31:24/<br>SDRAM RAS |

| CAS2*/SDCAS* | 198  | U12 | 0   | 4  | DRAM column strobe D23:16/<br>SDRAM RAS |

| CAS1*/SDWE*  | 197  | P13 | 0   | 8  | DRAM column strobe D15:08/<br>SDRAM RAS |

| CASO*/SD(AP) | 196  | R13 | 0   | 4  | DRAM column strobe D07:00/<br>SDRAM RAS |

| WE*          | 190  | R11 | 0   | 4  | Write enable                            |

| OE*          | 189  | P11 | 0   | 4  | Output enable                           |

Table 2: NET + 50 PQFP/BGA Chip Pinout - Chip select controller

### **Ethernet interface**

| Signal |           | PQFP | BGA | I/O | OD | Description |                 |

|--------|-----------|------|-----|-----|----|-------------|-----------------|

| MII    | 10BaseT   |      |     |     |    | МІІ         | 10BaseT         |

| MDC    | LB*       | 85   | D7  | 0   | 2  | MII clock   | Loopback enable |

| MDIO   | UTPSTP*   | 84†  | C7† | I/O | 2  | MII data    | Cable type      |

| TXCLK  | TXCLK     | 83   | B8  | 1   |    | TX clock    |                 |

| TXD0   | TXD       | 82   | A9  | 0   | 2  | TX data 0   | TX data         |

| TXD1   | PDN* (OD) | 81   | D8  | 0   | 2  | TX data 1   | Power down      |

Table 3: NET + 50 PQFP/BGA Chip Pinout - Ethernet interface

| Signal |          | PQFP | BGA | I/O | OD | Description   |                         |  |

|--------|----------|------|-----|-----|----|---------------|-------------------------|--|

| TXD2   | NTHRES   | 80   | C8  | 0   | 2  | TX data 2     | Normal threshold        |  |

| TXD3   | THIN     | 77   | D9  | 0   | 2  | TX data 3     | Enable Thinnet          |  |

| TXER   | LTE      | 76   | С9  | 0   | 2  | TX code error | Link test enable        |  |

| TXEN   | TXEN     | 75   | B10 | 0   | 2  | TX enable     |                         |  |

| COL    | TXCOL    | 74   | A11 | 1   |    | Collision     |                         |  |

| CRS    | RXCRS    | 73   | D10 | 1   |    | Carrier sense |                         |  |

| RXCLK  | RXCLK    | 72   | C10 | 1   |    | RX clock      |                         |  |

| RXD0   | RXD      | 71   | B11 | I   |    | RX data 0     | RX data                 |  |

| RXD1   | MANSENSE | 70   | A12 | 1   |    | RX data 1     | Sense jumper            |  |

| RXD2   | JABBER   | 69   | D11 | 1   |    | RX data 2     | Jabber                  |  |

| RXD3   | REVPOL   | 68   | C11 | 1   |    | RX data 3     | Reverse polarity        |  |

| RXER   | LINKPUL* | 67   | B12 | I   |    | RX error      | Link pulse<br>detection |  |

| RXDV   | AUTOMAN  | 66   | A13 | I   |    | RX data valid | 10B2 selected           |  |

Table 3: NET+50 PQFP/BGA Chip Pinout - Ethernet interface

## **MIC** interface

| Signal    |        |        | PQFP | BGA  | I/O | OD | Description            |

|-----------|--------|--------|------|------|-----|----|------------------------|

| IEEE 1284 | МІС    | GPIO   |      |      |     |    |                        |

| PDATA0    | PDATA0 | GPIOD0 | 200† | R14† | I/O | 2  | Parallel 1284/ENI/GPIO |

| PDATA1    | PDATA1 | GPIOD1 | 201† | P14† | I/O | 2  |                        |

| PDATA2    | PDATA2 | GPIOD2 | 202† | U13† | I/O | 2  |                        |

| PDATA3    | PDATA3 | GPIOD3 | 203† | R15† | I/O | 2  |                        |

| PDATA4    | PDATA4 | GPIOD4 | 204† | T14† | I/O | 2  |                        |

| PDATA5    | PDATA5 | GPIOD5 | 205† | U14† | I/O | 2  |                        |

| PDATA6    | PDATA6 | GPIOD6 | 206† | U15† | I/O | 2  |                        |

Table 4: NET + 50 PQFP/BGA Chip Pinout - MIC interface

| Signal   |         |        | PQFP | BGA  | I/O | OD | Description              |

|----------|---------|--------|------|------|-----|----|--------------------------|

| PDATA7   | PDATA7  | GPIOD7 | 207† | T15† | I/O | 2  |                          |

| POE1*    | PDATA8  |        | 2†   | T16† | I/O | 2  |                          |

| POE2*    | PDATA9  |        | 3†   | T17† | I/O | 2  |                          |

| POE3*    | PDATA10 |        | 4†   | R17† | I/O | 2  |                          |

| POE4*    | PDATA11 |        | 5†   | P15† | I/O | 2  |                          |

| PCLKC1   | PDATA12 |        | 6†   | R16† | I/O | 2  |                          |

| PCLKC2   | PDATA13 |        | 7†   | P17† | I/O | 2  |                          |

| PCLKC3   | PDATA14 |        | 8†   | N14† | I/O | 2  |                          |

| PCLKC4   | PDATA15 |        | 9†   | N15† | I/O | 2  |                          |

| PCLKD1   | PACK*   | GPIOF7 | 35   | G16  | I/O | 8  |                          |

| PCLKD2   | PEN*    | GPIOF6 | 10†  | P16† | I/O | 2  |                          |

| PCLKD3   | PINT1*  | GPIOF5 | 11   | N16  | I/O | 2  |                          |

| PCLKD4   | PINT2*  | GPIOF4 | 12   | M15  | I/O | 2  | Or ENI DMA output PDRQIO |

| ACK1*    | PA0     | GPIOH0 | 13   | M14  | 1   |    |                          |

| ACK2*    | PA1     | GPIOH1 | 14   | N17  | 1   |    |                          |

| ACK3*    | PA2     | GPIOH2 | 15   | M16  | 1   |    |                          |

| ACK4*    | PA3     | GPIOH3 | 16   | L15  | 1   |    |                          |

| BUSY1    | PA4     | GPIOH4 | 17   | L14  | 1   |    |                          |

| BUSY2    | PA5     | GPIOH5 | 18   | M17  | 1   |    |                          |

| BUSY3    | PA6     | GPIOH6 | 19   | L16  | 1   |    |                          |

| BUSY4    | PA7     | GPIOH7 | 20   | K15  | 1   |    |                          |

| PE1      | PA8     | GPIOG0 | 21   | K14  | 1   |    |                          |

| PE2      | PA9     | GPIOG1 | 22   | L17  | 1   |    |                          |

| PE3      | PA10    | GPIOG2 | 23   | K16  | 1   |    |                          |

| PE4      | PA11    | GPIOG3 | 24   | J15  | 1   |    |                          |

| PSELECT1 | PA12    | GPIOG4 | 25   | J14  | 1   |    |                          |

| PSELECT2 | PA13    | GPIOF3 | 28   | H15  | I/O | 2  | Or ENI DMA output PDRQI* |

Table 4: NET + 50 PQFP/BGA Chip Pinout - MIC interface

| Signal   |       |        | PQFP | BGA | I/O | OD | Description              |

|----------|-------|--------|------|-----|-----|----|--------------------------|

| PSELECT3 | PA14  | GPIOF2 | 29   | H14 | I/O | 2  | Or ENI DMA output PDRQO* |

| PSELECT4 | PA15  | GPIOG5 | 30   | J17 | 1   |    | Or ENI DMA input PDACK*  |

| FAULT1*  | PA16  | GPIOG6 | 31   | H16 | 1   |    |                          |

| FAULT2*  | PCS*  | GPIOG7 | 34   | H17 | I   |    |                          |

| FAULT3*  | PRW*  | GPIOF0 | 33   | G14 | I/O | 2  |                          |

| FAULT4*  | PBRW* | GPIOF1 | 32   | G15 | I/O | 2  |                          |

Table 4: NET + 50 PQFP/BGA Chip Pinout - MIC interface

## **UARTS-SPI-GPIO**

| Signal |             | PQFP            | BGA  | I/O | OD | Description       |                |

|--------|-------------|-----------------|------|-----|----|-------------------|----------------|

| PORTA7 | TXDA        | 38†             | G17† | I/O | 2  | SPI-S-TXD-O-A     | SPI-M-TXD-O-A  |

| PORTA6 | DTRA*/DRQ1* | 39†             | F16† | I/O | 2  |                   |                |

| PORTA5 | RTSA*       | 40†             | E15† | I/O | 2  |                   |                |

| PORTA4 | RXCA        | 41†             | E14† | I/O | 2  | SPI-S-CLK-I-A     | SPI-M-CLK-O-A* |

| PORTA3 | RXDA        | 42†             | F17† | I/O | 2  | SPI-S-RXD-I-A     | SPI-M-RXD-I-A  |

| PORTA2 | DSRA*/DAK1* | 43†             | E16† | I/O | 2  |                   |                |

| PORTA1 | CTSA*       | 44†             | D15† | I/O | 2  |                   |                |

| PORTA0 | DCDA*/DON1* | 45†             | D14† | I/O | 2  |                   |                |

| PORTB7 | TXDB        | 46 <sup>†</sup> | E17† | I/O | 2  | SPI-S-TXD-O-B     | SPI-M-TXD-O-B  |

| PORTB6 | DTRB*/DRQ2* | 47†             | C15† | I/O | 2  |                   |                |

| PORTB5 | RTSB*       | 48†             | D16† | I/O | 2  | Reject* Ethernet  | packet         |

| PORTB4 | RXCB        | 49†             | D17† | I/O | 2  | SPI-S-CLK-I-B     | SPI-M-CLK-O-B* |

| PORTB3 | RXDB        | 50†             | C17† | I/O | 2  | SPI-S-RXD-I-B     | SPI-M-RXD-O-B  |

| PORTB2 | DSRB*/DAK2* | 51 <sup>†</sup> | C16† | I/O | 2  |                   |                |

| PORTB1 | CTSB*       | 54†             | B16† | I/O | 2  | RPSF* Ethernet fi | rame boundary  |

| PORTB0 | DCDB*/DON2* | 55 <sup>†</sup> | A16† | I/O | 2  |                   |                |

Table 5: NET+50 PQFP/BGA Chip Pinout - UARTS-SPI-GPIO

| Signal |            | PQFP            | BGA  | I/O | OD | Description  |              |

|--------|------------|-----------------|------|-----|----|--------------|--------------|

| PORTC7 | TXCA       | 56†             | A15† | I/O | 4  | SPI-S-EN-I-A | SPI-M-EN-O-A |

| PORTC6 | RIA*/IRQO* | 57 <sup>†</sup> | C14† | I/O | 4  |              |              |

| PORTC5 | ТХСВ       | 58†             | B15† | I/O | 4  | SPI-S-EN-I-B | SPI-M-EN-O-B |

| PORTC4 | RIB*       | 59†             | A14† | I/O | 4  |              |              |

| PORTC3 | AMUX       | 60†             | D13† | I/O | 8  | Interrupt 3  |              |

| PORTC2 |            | 61 <sup>†</sup> | C13† | I/O | 8  | Interrupt 2  |              |

| PORTC1 |            | 62†             | B14† | I/O | 8  | Interrupt 1  |              |

| PORTC0 |            | 63†             | B13† | I/O | 8  | Interrupt 0  |              |

Table 5: NET + 50 PQFP/BGA Chip Pinout - UARTS-SPI-GPIO

## Clock generation/system reset

| Signal         | PQFP | BGA  | I/O | OD | Description                    |

|----------------|------|------|-----|----|--------------------------------|

| XTAL1          | 178  | U7   | 1   |    | Crystal oscillator circuit     |

| XTAL2          | 179  | Т8   | 0   |    |                                |

| PLLVDD (2.5V)  | 182  | U8   |     |    | 2.5 V PLL clean power          |

| PLLLPF         | 181  | P9   |     |    | PLL loop filter capacitor      |

| PLLVSS         | 180  | R9   |     |    | PLL clean ground               |

| PLLTST* (2.5V) | 177† | P8†  | 1   |    | PLL test mode                  |

| BISTEN*        | 184† | R10† | 1   |    | Enable internal BIST operation |

| SCANEN*        | 185† | P10† | 1   |    | Enable internal SCAN testing   |

| System reset   |      |      |     |    |                                |

| RESET*         | 158† | T2†  | I   |    | System reset                   |

Table 6: NET + 50 PQFP/BGA Chip Pinout - Clock generation/system reset

## JTAG port for ARM core

| Signal | PQFP | BGA | I/O | OD | Description                                    |

|--------|------|-----|-----|----|------------------------------------------------|

| TDI    | 171† | T6† | 1   |    | Test data in                                   |

| TDO    | 170  | U5  | 0   | 2  | Test data out                                  |

| TMS    | 172† | R7† | I   |    | Test mode select                               |

| TRST*  | 174  | R8  | I   |    | Test mode reset. This is a current input sink. |

| TCK    | 173  | P7  | 1   |    | Test mode clock                                |

Table 7: NET+50 PQFP/BGA Chip Pinout - JTAG port for ARM core

## **Power supply**

| Signal                         | Mode | Pin/Ball Number            | Description                           |

|--------------------------------|------|----------------------------|---------------------------------------|

| V <sub>CC</sub> DC 3.3V DC     | BGA  | F15, B17, C12, A2, M2, U9  | I/O steady state (6 pairs)            |

|                                | PQFP | 36, 52, 64, 104, 143, 186  |                                       |

| V <sub>SS</sub> DC GND Returns | BGA  | F14, A17, D12, A1, N3, U10 |                                       |

|                                | PQFP | 37, 53, 65, 105, 144, 188  |                                       |

| V <sub>CC</sub> AC 3.3V        | BGA  | A8, E1, T1, U16            | I/O switching (4 pairs <sup>a</sup> ) |

|                                | PQFP | 86, 118, 156, 208          |                                       |

| V <sub>SS</sub> AC GND Returns | BGA  | B7, F2, U1, U17            |                                       |

|                                | PQFP | 87, 119, 157, 1            |                                       |

| V <sub>DD</sub> CO 2.5V        | BGA  | K17, A10, H1, T7           | Core power (4 pairs)                  |

|                                | PQFP | 26, 78, 130, 175           |                                       |

| V <sub>SS</sub> CO GND Returns | BGA  | J16, B9, J2, U6            |                                       |

|                                | PQFP | 27, 79, 131, 176           |                                       |

Table 8: NET + 50 PQFP/BGA Chip Pinout - Power supply

#### Signal description summary

| Signal                        | Mode | Pin/Ball Number | Description                   |

|-------------------------------|------|-----------------|-------------------------------|

| PLLV <sub>DD</sub> 2.5V       | BGA  | U8              | PLL bead filtered clean power |

|                               | PQFP | 182             |                               |

| PLLV <sub>SS</sub> GND Return | BGA  | R9              |                               |

|                               | PQFP | 180             |                               |

| PORV <sub>SS</sub> GND        | BGA  | Т9              | Powerup reset GND reference   |

|                               | PQFP | 183             |                               |

#### Table 8: NET + 50 PQFP/BGA Chip Pinout - Power supply

a. Digi recommends that you use separate power pairs for AC and DC power, to prevent the noise in the AC power buses from reaching the DC power buses. Digi recommends and uses a ferrite bead to filter the AC power pins.

## Signal description summary

The signal description summary defines and briefly describes the signals included in the interfaces in the NET+50 chip. The description tables in the section are presented in the same order as the NET+50 chip pinout tables. For details about any of the signals/pinouts, see the appropriate chapter:

| Interface                          | Chapter                                  |

|------------------------------------|------------------------------------------|

| System bus                         | Chapter 8, "Memory Controller Module"    |

| Chip select controller             | Chapter 8, "Memory Controller Module"    |

| Ethernet MII                       | Chapter 10, "Ethernet Controller Module" |

| MIC                                | Chapter 12, "MIC Controller Module"      |

| UARTS-SPI-GPIO; GPIO ports A, B, C | Chapter 6, "The GEN Module"              |

| Clock generation                   | Chapter 6, "The GEN Module"              |

The JTAG Port for ARM Core (ARM Debugger) and Power sections are addressed fully in their respective discussions.

## System bus interface

The NET+50 chip uses the system bus interface to interface with memory-mapped peripheral devices such as flash, SRAM, and DRAM.

| Code  | Definition                 | Description                                                                                                                                                           |

|-------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK  | Bus clock                  | Provides the bus clock. All system bus interface signals are referenced to the BCLK signal.                                                                           |

| ADDR  | Address bus                | Identifies the address of the peripheral being addressed by the current bus master. The address bus is bi-directional.                                                |

| DATA  | Data bus                   | Provides the data transfer path between the NET + 50 chip and external peripheral devices. The data bus is bi-directional.                                            |

| TS*   | Transfer start             | NO CONNECT                                                                                                                                                            |

| BE*   | Byte enable                | Identifies which 8-bit bytes of the 32-bit data bus are active during any given system bus memory cycle. The BE* signals are active low and bi-directional.           |

| RW*   | Read/write<br>indicator    | Indicates the direction of the system bus memory cycle. RW* high identifies a read operation; RW* low identifies a write operation. The RW* signal is bi-directional. |

| TA*   | Transfer<br>acknowledge    | Indicates the end of the current system bus memory cycle. This signal is bi-directional.                                                                              |

| TEA*  | Transfer error acknowledge | Indicates an error termination or burst cycle termination. TEA* is bi-directional. The NET+50 chip or the external peripheral can drive the TEA* signal.              |

| BR*   | Bus request                | NO CONNECT                                                                                                                                                            |

| BG*   | Bus grant                  | NO CONNECT                                                                                                                                                            |

| BUSY* | Bus busy                   | NO CONNECT                                                                                                                                                            |

Table 9: System bus interface signal description

## Chip select controller

The NET+50 chip supports five unique chip select configurations.

| Code                                 | Definition                                                            | Description                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS0*<br>CS1*<br>CS2*<br>CS3*<br>CS4* | Chip select 0 Chip select 1 Chip select 2 Chip select 3 Chip select 4 | Unique chip select outputs supported by the NET $+50$ chip. Each chip select can be configured to decode a portion of the available address space and can address a maximum of 256 Mbytes of address space. The chip selects are configured using registers in the memory module.                                     |

| CAS0*<br>CAS1*<br>CAS2*<br>CAS3*     | Column<br>address strobe<br>signals                                   | Activated when an address is decoded by a chip select module configured for DRAM mode. The CAS* signals are active low and provide the column address strobe function for DRAM devices.  The CAS* signals also identify which 8-bit bytes of the 32-bit data bus are active during any given system bus memory cycle. |

| WE*                                  | Write enable                                                          | Active low signal indicating that a memory write cycle is in progress. This signal is activated only during write cycles to peripherals controlled by one of the chip selects in the memory module.                                                                                                                   |

| OE*                                  | Output enable                                                         | Active low signal indicating that a memory read cycle is in progress. This signal is activated only during read cycles from peripherals controlled by one of the chip selects in the memory module.                                                                                                                   |

Table 10: Chip select controller signal description

#### Ethernet MII

The Ethernet MII (Media Independent Interface) provides the connection between the Ethernet PHY and the MAC (Media Access Controller).

| Code  | Definition               | Description                                                                                                                      |

|-------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| MDC   | Management<br>data clock | Provides the clock for the MDIO serial data channel. The MDC signal is a NET + 50 chip output. The maximum frequency is 2.5 MHz. |

| MDIO  | Management<br>data IO    | A bi-directional signal that provides a serial data channel between the NET + 50 chip and the external Ethernet PHY module.      |

| TXCLK | Transmit clock           | An input to the NET + 50 chip from the external PHY module. TXCLK provides the synchronous data clock for transmit data.         |

Table 11: Ethernet MII signal description

| Code  | Definition            | Description                                                                                                                         |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| TXD3  | Transmit data         | Nibble bus used by the NET + 50 chip to drive data to the external Ethernet PHY.                                                    |

| TXD2  | signals               | All transmit data signals are synchronized to TXCLK. In ENDEC mode, only TDXO is used for transmit data.                            |

| TXD1  |                       | TDAO IS USED FOI CHARSTIIC data.                                                                                                    |

| TXD0  |                       |                                                                                                                                     |

| TXER  | Transmit coding error | Output asserted by the NET $\pm$ 50 when an error has occurred in the transmit data stream.                                         |

| TXEN  | Transmit<br>enable    | Asserted when the chip drives valid data on the TXD outputs. This signal is synchronized to TXCLK.                                  |

| COL   | Transmit collision    | Input signal asserted by the external Ethernet PHY when a collision is detected.                                                    |

| CRS   | Receive carrier sense | Asserted by the external Ethernet PHY whenever the receive medium is non-idle.                                                      |

| RXCLK | Receive clock         | An input to the NET + 50 chip from the external PHY module. The receive clock provides the synchronous data clock for receive data. |

| RXD3  | Receive data          | Nibble bus used by the NET + 50 chip to input receive data from the external                                                        |

| RXD2  | signals               | Ethernet PHY. All receive data signals are synchronized to RXCLK. In ENDEC                                                          |

| RXD1  |                       | mode, only RXD0 is used for receive data.                                                                                           |

| RXD0  |                       |                                                                                                                                     |

| RXER  | Receive error         | Input asserted by the external Ethernet PHY when the Ethernet PHY encounters invalid symbols from the network.                      |

| RXDV  | Receive data valid    | Input asserted by the external Ethernet PHY when the Ethernet PHY drives valid data on the RXD inputs.                              |

Table 11: Ethernet MII signal description

#### MIC interface

The NET+50 chip uses the MIC interface to interface with other embedded computer systems. The MIC interface provides various modes: GPIO, IEEE 1284, shared RAM, and FIFOs.

The MIC interface can be configured to operate in GPIO, IEEE 1284, or ENI host mode — but never at the same time. The ENI host mode supports shared RAM and FIFO interfaces.

If this port is not used, it must be defaulted during bootstrap to a known value, such as 100 (ENI Shared-16 RAM Mode), by providing input current sink resistors on NET+50

pins A22, A21, and A20. Unused input pins must be terminated according to the NET+50 minimum configuration.

When the MIC interface is set to GPIO or 1284 Mode, unused inputs in each of these modes must be terminated.

This section provides details for each MIC interface mode.

#### IEEE 1284 mode

| Code                                 | Definition                                                                              | Description                                                                                                                                                                                                                                                                                               |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PDATA                                | 1284 data bus                                                                           | A bi-directional data bus that interfaces the NET $\pm$ 50 chip with the external 1284 port data and control transceivers. The NET $\pm$ 50 chip interfaces only with a single 1284 port at a time.                                                                                                       |  |  |

| POE1* POE2* POE3* POE4*              | Output enables:<br>1284 Channel 1<br>1284 Channel 2<br>1284 Channel 3<br>1284 Channel 4 | Channel output enable signals that control the output enable for each specific port data register.                                                                                                                                                                                                        |  |  |

| PCLKC1<br>PCLKC2<br>PCLKC3<br>PCLKC4 | Control clocks:<br>1284 Channel 1<br>1284 Channel 2<br>1284 Channel 3<br>1284 Channel 4 | Channel control clock signals that are driven by the NET + 50 chip to load the 1284 data bus outputs into the various 1284 control transceivers. Only one channel control clock is active at any moment in time. The channel control clocks are never active at the same time as any channel data clocks. |  |  |

| PCLKD1<br>PCLKD2<br>PCLKD3<br>PCLKD4 | Data clocks:<br>1284 Channel 1<br>1284 Channel 2<br>1284 Channel 3<br>1284 Channel 4    | Channel data clock signals that are driven by the NET + 50 chip to load the 1284 data bus outputs into the various 1284 data transceivers. Only one channel data clock is active at any moment in time. The channel data clocks are never active at the same time as any channel control clocks.          |  |  |

| ACK1*<br>ACK2*<br>ACK3*<br>ACK4*     | Acknowledge:<br>1284 Channel 1<br>1284 Channel 2<br>1284 Channel 3<br>1284 Channel 4    | Channel ACK inputs to the NET + 50 chip from the external IEEE 1284 port. The ACK input meaning changes as the IEEE 1284 operational mode changes.  Note: For additional information about IEEE 1284 operational modes, see your IEEE documentation.                                                      |  |  |

Table 12: MIC IEEE 1284 mode signal description

| Code                                    | Definition                                                                       | Description                                                                                                                                                                                                                                                                      |

|-----------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

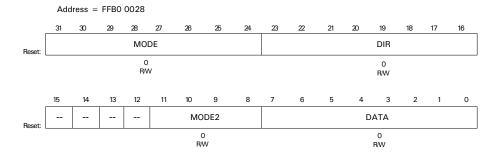

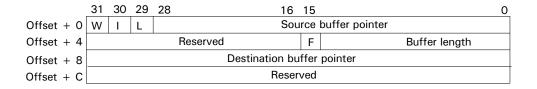

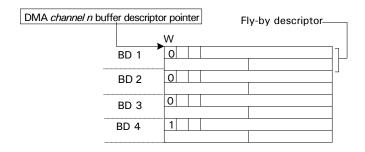

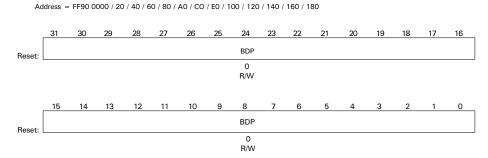

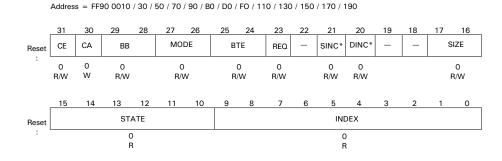

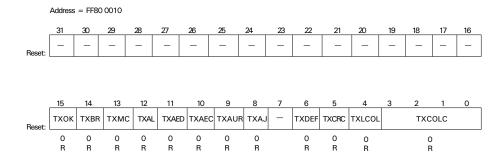

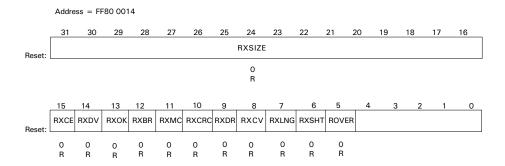

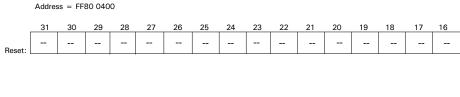

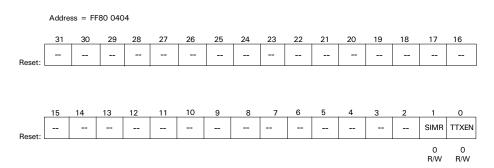

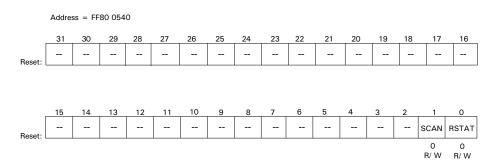

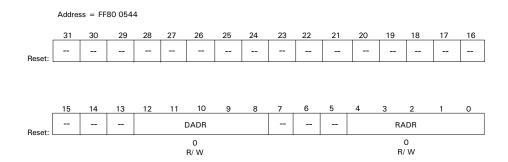

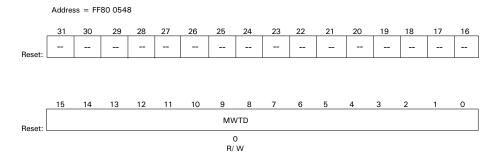

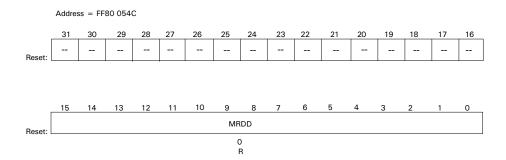

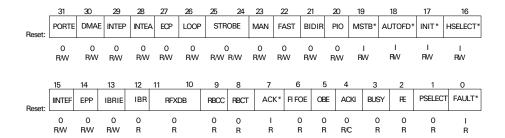

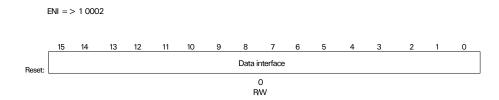

| BUSY1* BUSY2* BUSY3* BUSY4*             | BUSY:<br>1284 Channel 1<br>1284 Channel 2<br>1284 Channel 3<br>1284 Channel 4    | Channel BUSY inputs to the NET + 50 chip from the external IEEE 1284 port. The BUSY input meaning changes as the IEEE 1284 operational mode changes.  Note: For additional information about IEEE 1284 operational modes, see your IEEE documentation.                           |